|                             |                                                                                               |                                     |

|-----------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------|

|                             | <b>FONCTION TRAITER L'INFORMATION</b><br><i>Aspect Fonctionnel ; Physique ; Technologique</i> | <br>@.EZ@HR@OUI                     |

| <b>Cours ; Applications</b> |                                                                                               | 2 <sup>eme</sup> STM<br>Doc : élève |

## CONVERSION DE DONNÉES

### I- DÉFINITION :

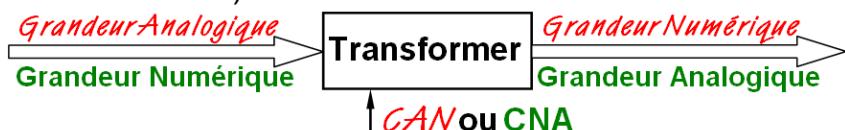

En électronique, la conversion de données a pour but de **transformer** une **grandeur électrique ou numérique** en une autre **grandeur numérique ou électrique** elle aussi, dans le but d'en faciliter l'exploitation. Cette technique est aujourd'hui couramment employée dans les appareils à affichage numérique et dans les systèmes de traitement numérique de l'information (incluant les microprocesseurs et les micro-ordinateurs).

Le SADT de convertisseur :

#### a- Grandeur analogique :

C'est une grandeur qui varie dans le temps de façon continue et qui prend une infinité de valeurs.

#### b- Grandeur numérique :

C'est une grandeur qui varie dans le temps de façon discontinue, par exemple le nombre de voyageurs franchissant un portillon, l'indication d'une horloge à affichage numérique.

C'est donc toujours un nombre entier. En électronique, on utilise surtout des grandeurs numériques formées de 0 et de 1 logique, qui présentent de nombreux avantages par rapport aux grandeurs analogiques (tension ou courant) : insensibilité aux bruits, aux distorsions, facilité de mémorisation et de restitution.

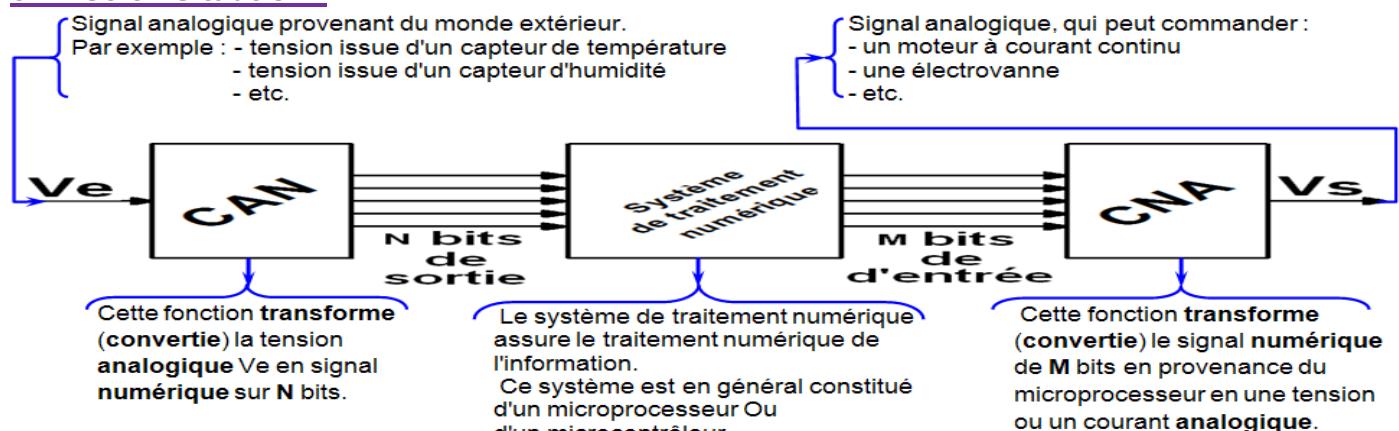

#### c- Mise en situation :

### II- CARACTÉRISTIQUES DES CONVERTISSEURS :

#### Caractéristique de transfert :

La caractéristique d'un convertisseur (numérique / analogique ou analogique / numérique) est la courbe représentant la grandeur de sortie en fonction de la grandeur d'entrée.

#### Convertisseur Analogique / Numérique (CAN)

#### Convertisseur Numérique / Analogique (CNA)

|                             |                                                                                               |                                     |

|-----------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------|

|                             | <b>FONCTION TRAITER L'INFORMATION</b><br><i>Aspect Fonctionnel ; Physique ; Technologique</i> | <br>@.EZ@HR@OUI                     |

| <b>Cours ; Applications</b> |                                                                                               | 2 <sup>eme</sup> STM<br>Doc : élève |

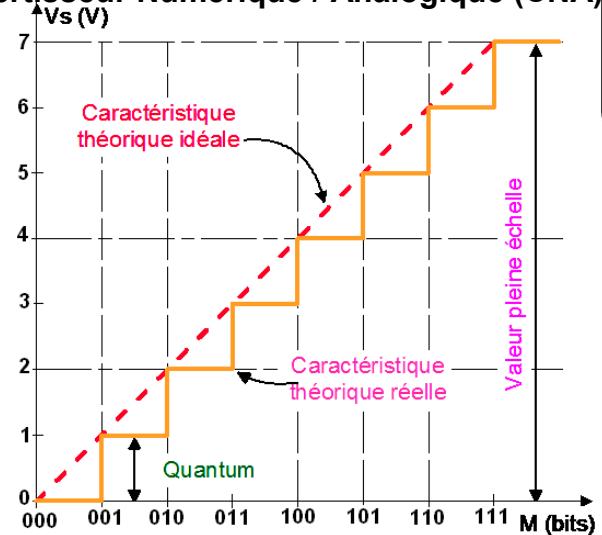

### III- Convertisseur Numérique-Analogique (CNA)

#### a- Principe :

Un Convertisseur Numérique-Analogique, ou **CNA**, est un montage transformant une information numérique (binaire en général) en un signal analogique (tension).

Un **CNA** peut convertir un quartet (ou un octet, ou plus) issu de circuits logiques en une tension proportionnelle à la valeur décimale du nombre binaire converti.

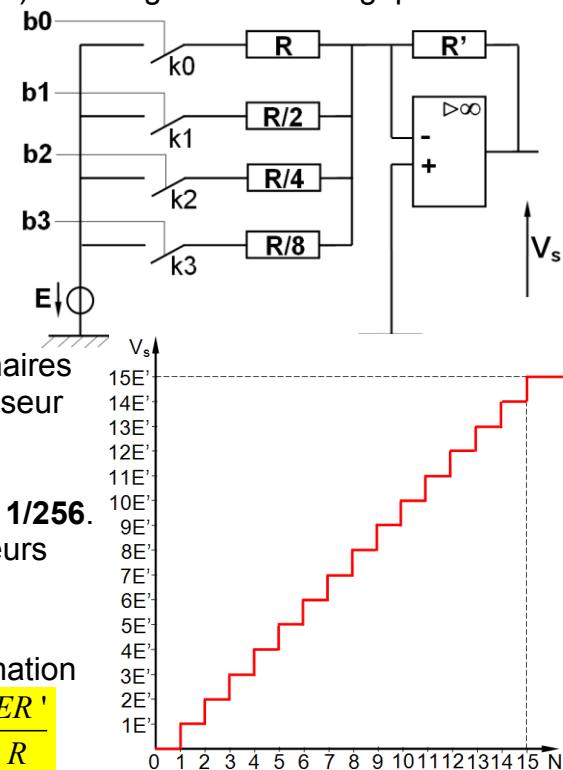

Un registre binaire à quatre éléments binaires (par exemple) fournit quatre tensions permettant de commander quatre interrupteurs **k0, k1, k2 et k3**. La conversion de cette information numérique (un interrupteur **k ouvert** est à l'état **0**, **k fermé** est à l'état **1**) en une grandeur analogique est réalisée par le montage ci-dessous.

Le montage est un sommateur et la tension **V<sub>s</sub>** s'écrit :

$$V_s = \frac{ER'}{R} [8 \cdot (k_3) + 4 \cdot (k_2) + 2 \cdot (k_1) + 1 \cdot (k_0)]$$

#### b- Résolution :

La résolution est l'inverse du nombre de combinaisons binaires que le convertisseur est capable de convertir. Un convertisseur à 4 éléments binaires possède 16 combinaisons à l'entrée (de **0000** à **1111**). Sa résolution est **1/16**.

La résolution d'un convertisseur à 8 éléments binaires est **1/256**.

Si dans l'exemple tous les bits sont à **1**, tous les interrupteurs

sont fermés et **V<sub>s</sub>** s'écrit :  $V_s = \frac{ER'}{R} [8+4+2+1] = 15 \frac{ER'}{R}$

Si seul le bit **b0** est égal à **1** et les autres bites à **0**, l'information

d'entrée vaut **0001** (soit **1** en décimale) et **V<sub>s</sub>** s'écrit :  $V_s = \frac{ER'}{R}$

C'est donc la plus petite valeur non nulle que peut transmettre le convertisseur.

La tension **E** s'appelle tension de référence et la valeur  $15 \frac{ER'}{R}$  donne la tension de pleine échelle

**FS** (Full Scale).

L'accroissement d'une unité du nombre d'entrées fournit, en principe, un accroissement de la tension de sortie **ΔV<sub>s</sub>**.

$$\Delta V_s = \frac{ER'}{R} = E'$$

• **Remarque :** • La résolution est définie en % de la Pleine Échelle (**FULL SCALE** ou **FS**).

- La résolution est liée au quantum.

- La valeur du quantum dépend de la tension Pleine Échelle (**PE, FS**), elle est donnée par la relation :

$$q = \frac{\text{Valeur Pleine échelle}}{2^{\text{nombre de bits}}} = \frac{\text{Valeur}_{\text{MAX}} - \text{Valeur}_{\text{min}}}{2^{\text{nombre de bits}}}$$

|                             |                                                                                               |                                     |

|-----------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------|

|                             | <b>FONCTION TRAITER L'INFORMATION</b><br><i>Aspect Fonctionnel ; Physique ; Technologique</i> | <br>@.EZ@HR@OUI                     |

| <b>Cours ; Applications</b> |                                                                                               | 2 <sup>eme</sup> STM<br>Doc : élève |

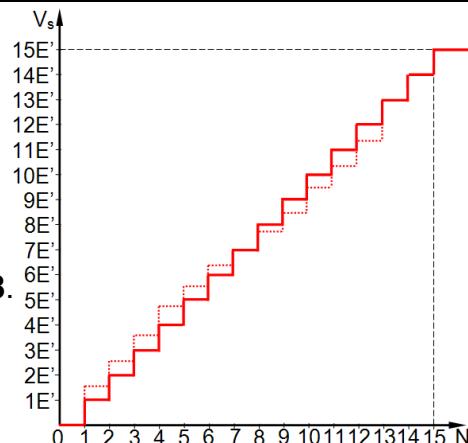

### c- Linéarité :

La caractéristique de transfert  $V_s = f(N)$  du **CNA** est donc théoriquement constituée de marche d'escalier identique (voir courbe ci-dessus).

En pratique, les circuits fournissant les tensions appliquées sur les interrupteurs de la page précédente ne sont pas parfaits.

Les résistances placées à l'entrée de l'amplificateur intégré ne peuvent être rigoureusement dans les rapports **1, 1/2, 1/4, 1/8**.

Il en résulte des dissymétries sur la caractéristique de transfert du **CNA** qui caractérisent le défaut de non-linéarité du convertisseur : la courbe réelle en trait pointillés diffère de la courbe idéale qui est en continu.

### d- Temps de conversion - temps d'établissement : (Settling time)

C'est le maximum que peut atteindre la durée de conversion numérique-analogique. Le cas le plus défavorable correspond au passage de **N = 0000** à **N = 1111** puisque les quatre interrupteurs doivent tous commuter.

Les commutations ne sont pas nécessairement simultanées, des tensions parasites peuvent alors apparaître avant que la tension  $V_s$  ne se stabilise à sa valeur finale.

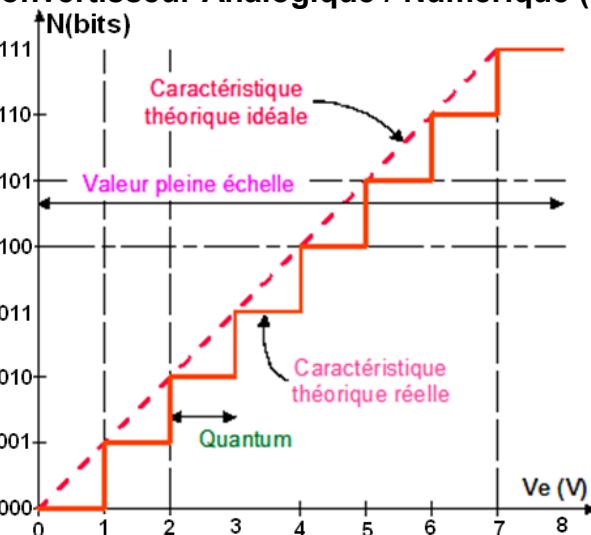

## IV- Convertisseur Analogique-Numérique (CAN)

### a- Principe :

Un **Convertisseur Analogique-Numérique**, ou CAN, est un montage transformant une tension appliquée à son entrée en une suite ordonnée de 0 et de 1 logiques apparaissant sur ses sorties.

L'ensemble des sorties du convertisseur permet de constituer un nombre binaire (Quartet, Octet...)

### b- Résolution :

La résolution est l'écart minimal de tension d'entrée qui entraîne un changement de code d'une unité en sortie.

- **Remarque :**

- La résolution est liée au quantum.

- La valeur du quantum dépend de la tension Pleine Échelle (**PE**, **FS**), elle est donnée par la relation :

$$q = \frac{\text{Valeur Pleine échelle}}{(2^{\text{nombre de bits}} - 1)} = \frac{\text{Valeur}_{\text{MAX}} - \text{Valeur}_{\text{min}}}{(2^{\text{nombre de bits}} - 1)}$$

### c- Linéarité :

La caractéristique de transfert  $N = f(V_e)$  est encore une fonction en escalier, comme pour un **CNA**. Les imperfections des composants du montage convertisseur font que les largeurs des marches ne sont pas égales.

Cette dissymétrie caractérise la non-linéarité du montage.

### d- Temps de conversion - temps d'établissement : (Settling time)

Une conversion analogique-numérique nécessitant un temps de comptage, le temps de conversion sera nécessairement plus élevé que celui d'un convertisseur numérique-analogique qui n'est tributaire que du basculement de quelques interrupteurs. Il peut atteindre 100 ms, voire 500 ms dans certains montages.

|                             |                                                                                               |                                                  |

|-----------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------|

|                             | <b>FONCTION TRAITER L'INFORMATION</b><br><i>Aspect Fonctionnel ; Physique ; Technologique</i> | <br><b>@.EZ@HR@OUI</b>                           |

| <b>Cours ; Applications</b> |                                                                                               | <b>2<sup>eme</sup> STM</b><br><b>Doc : élève</b> |

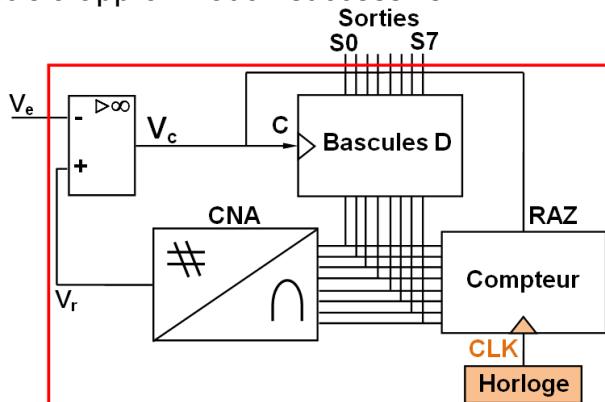

## V- Étude théorique d'un CAN 8 bits :

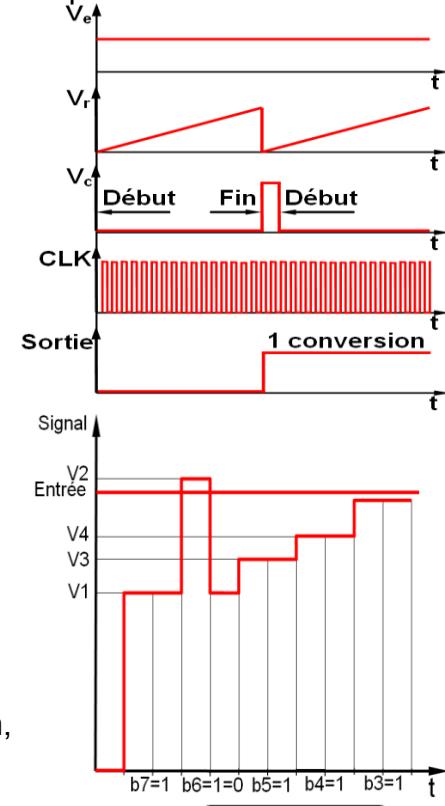

Une horloge interne génère des impulsions d'horloge. Celles-ci sont envoyées sur un compteur binaire à 8 étages. Les sorties binaires du compteur sont reliées à un convertisseur **CNA**.

Ce convertisseur va produire une tension  $V_r$  proportionnelle au mot binaire issu du compteur.

Un comparateur de tension compare la tension d'entrée  $V_e$  avec celle issu du **CNA**  $V_r$ .

Lorsque  $V_e = V_r$ ,  $V_c$  passe à l'état logique 1. À cet instant les bascules **D** mémorisent le mot binaire du compteur qui représente  $V_r$  mais aussi  $V_e$ .

À cet instant, le mot binaire est présent en sortie et le restera jusqu'à la prochaine conversion.

Pour recommencer une nouvelle conversion,  $V_c$  remet également le compteur à zéro.

Ceci est un principe très simplifié d'une conversion analogique-numérique.

Dans le cas du **ADC0804** le compteur est remplacé par un registre à approximation successive

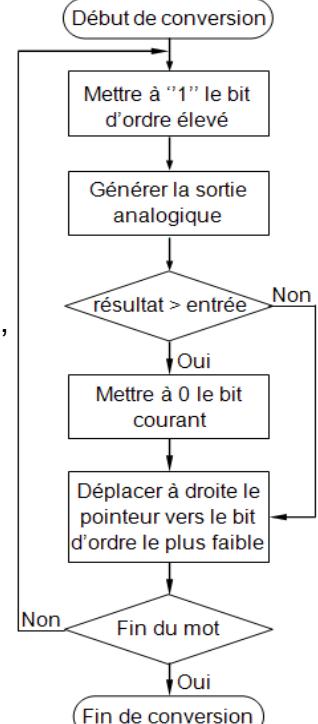

### a- Approximations successives :

La technique des approximations successives est la plus utilisée avec les microprocesseurs par sa grande vitesse, et sa haute résolution.

Le principe de la méthode est de générer une estimation initiale de la valeur à entrer, de la convertir en analogique puis de la comparer avec la valeur réelle. Selon le résultat de la comparaison, cette estimation initiale est diminuée ou augmentée.

Par exemple, si l'on suppose une approximation sur 8 bits, l'estimation initiale pourrait être 1000 000.

Si la valeur réelle est plus grande que l'équivalent analogique de 1000 000, on met à 1 le bit suivant (b6). L'estimation est alors 1100 000.

Si elle est à nouveau trop petite, la prochaine estimation sera 1110 000.

Si l'entrée est maintenant plus petite que l'approximation courante, le bit qui a été mis à 1 en dernier sera mis à 0 et on essaiera le bit suivant. L'estimation suivante sera 1101 000 et ainsi de suite.

En résumé, lorsque l'entrée réelle est plus grande que l'estimation, le bit courant est laissé à 1 et on essaie le suivant. Lorsqu'elle est inférieure, on met à 0 le bit courant et on essaie le suivant.

### b- Algorithme d'approximations successives :

Faire : - mettre à 1 le bit d'ordre élevé,

- générer la sortie analogique **CNA**,

- si le résultat est supérieur à l'entrée alors mettre à 0 le bit courant,

- déplacer à droite le pointeur vers le bit le plus faible jusqu'à la fin du mot.

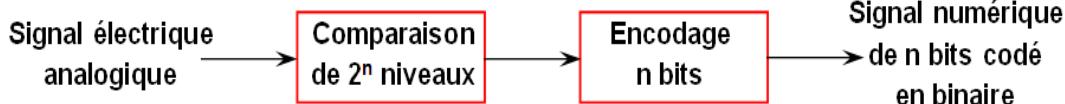

## **VI- Étude théorique d'un CAN FLASH 2 bits :**

### **a- Principe :**

Pour numériser l'information analogique, on utilise une série de comparateurs qui réagissent sur un niveau donné de la tension analogique.

Dans l'exemple, on dispose de 4 niveaux différents  $1/4$  de  $V_{ref}$ ,  $1/2$  de  $V_{ref}$ ,  $3/4$  de  $V_{ref}$  et  $V_{ref}$ . L'information est numérisée mais pas encore exploitable car il y a autant de sorties que de niveaux et pour un convertisseur 8 bits cela représente 256 sorties ! Il est donc indispensable d'encoder ces niveaux pour obtenir un binaire naturel plus compact.

Le schéma fonctionnel suivant résume cette démarche.

Le gros avantage de cette technique est la vitesse. En effet la durée de conversion est limitée à la vitesse de réaction du comparateur plus la durée de transition des portes logiques soit une durée totale de traitement variant de la microseconde à quelques dizaines de nanosecondes.

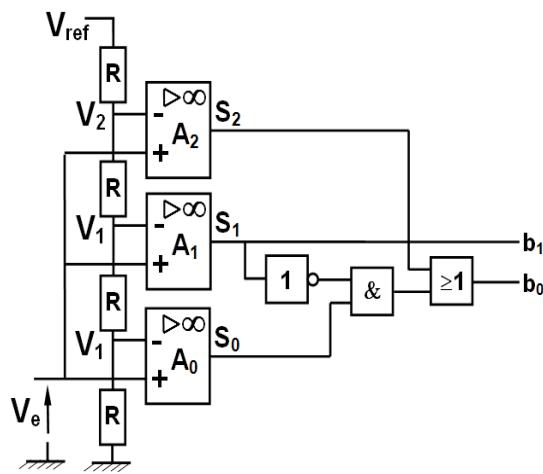

### b- Schéma structurel :

On a besoin de  $2^n$  résistances identiques qui fixeront les niveaux de tension à partir d'une tension  $V_{ref}$  et  $2^n-1$  comparateur.  $V_r$

Chaque comparateur va changer d'état lorsque la tension d'entrée sera supérieure au niveau de tension de l'entrée inverseuse du comparateur. Il en résulte la table de vérité donnée ci-dessous.

À partir de cette table de vérité, on sort l'équation logique des sorties. On les simplifie puis on réalise le **logigramme** représentant notre encodeur.

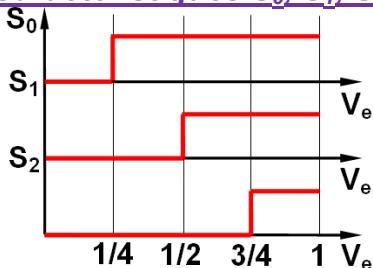

### c- Caractéristiques $S_0, S_1, S_2 = f(V_e)$

#### **d- Table de vérité :**

|                   | $S_2$ | $S_1$ | $S_0$ | $b_1$ | $b_0$ |

|-------------------|-------|-------|-------|-------|-------|

| $0 < V_e < 1/4$   | 0     | 0     | 0     | 0     | 0     |

| $1/4 < V_e < 1/2$ | 0     | 0     | 1     | 0     | 1     |

| $1/2 < V_e < 3/4$ | 0     | 1     | 1     | 1     | 0     |

| $3/4 < V_e < 1$   | 1     | 1     | 1     | 1     | 1     |

## f- Équations logiques :

$$\mathbf{b}_0 = S_0 \cdot \overline{S}_1 \cdot \overline{S}_2 + S_0 \cdot S_1 \cdot S_2$$

$$\mathbf{b}_0 = \mathbf{S}_0 \cdot \mathbf{S}_1 \cdot \overline{\mathbf{S}}_2 + \mathbf{S}_0 \cdot \mathbf{S}_1 \cdot \mathbf{S}_2$$

## e- Table de Karnaugh

| $b_1$ | $S_1, S_0$ |    |    |    |

|-------|------------|----|----|----|

|       | 00         | 01 | 11 | 10 |

| $S_2$ | 0          | 0  | 1  | x  |

|       | 1          | x  | x  | 1  |

$b_1 = S_1$

| $b_0$                             | $S_1, S_0$ |    |    |    |   |

|-----------------------------------|------------|----|----|----|---|

|                                   | 00         | 01 | 11 | 10 |   |

| $S_2$                             | 0          | 0  | 1  | 0  | x |

|                                   | 1          | x  | x  | 1  | x |

| $b_0 = S_0 \cdot \bar{S}_1 + S_2$ |            |    |    |    |   |

## **d- Équations logiques simplifiées :**

$$b_1 = s_1$$

$$b_0 = S_0 \cdot \bar{S}_1 + S_2$$