## Exercice : CAN à approximations successives

Dans ce type de convertisseur la tension à convertir est comparée successivement à des tensions de référence connues un peu comme lorsque l'on pèse une marchandise sur le plateau d'une balance. A cause de cette analogie ce convertisseur est aussi appelé **convertisseur à pesée**.

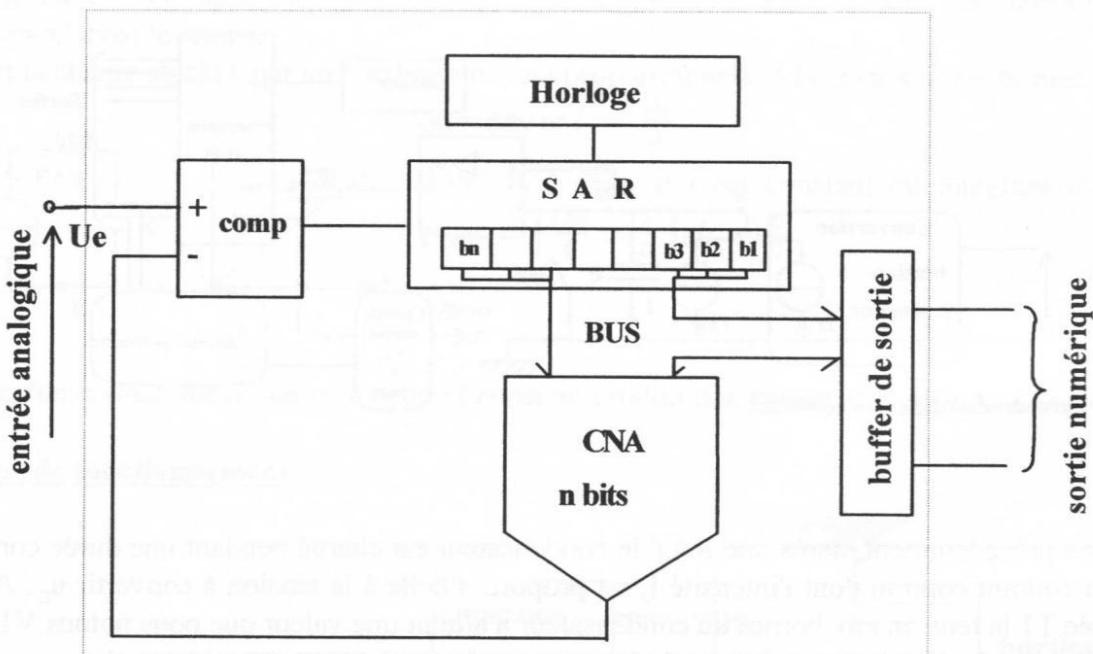

Un schéma fonctionnel interne simplifié est représenté ci dessous:

### Principe de fonctionnement :

Sous le cadencement d'une horloge, le **Registre à Approximation Successives (SAR)** positionne à 1 un de ses bits en commençant par le bit de poids fort. La donnée binaire est convertie en analogique par un convertisseur numérique analogique et est comparée à la tension à convertir. Si la tension analogique à convertir est plus élevée alors le bit mis à un est validé sinon il est remis à zéro et le bit de poids inférieur est mis à un pour un nouveau cycle de comparaison . Au bout de n cycles (pour un convertisseur n bits ) tous les bits du registre sont positionnés et représentent le résultat de la conversion.

Afin de concrétiser ce principe de fonctionnement on l'appliquera à un exemple: **Conversion d'une tension égale à 6.5V par un convertisseur 8 bits dont la tension de référence est de 10 volts**

Quelle est la valeur du quantum?

### 1ère comparaison

| essai du bit 8       | tension analogique associée | résultat comparaison | bit conservé         | bit rejeté           |

|----------------------|-----------------------------|----------------------|----------------------|----------------------|

| <input type="text"/> | <input type="text"/>        | <input type="text"/> | <input type="text"/> | <input type="text"/> |

**2ème comparaison**

essai du bit 7

tension analogique associée

résultat comparaison

bit conservé

bit rejeté

**3ème comparaison**

essai du bit 6

tension analogique associée

résultat comparaison

bit conservé

bit rejeté

**4ème comparaison**

essai du bit 5

tension analogique associée aux bit

résultat comparaison

bit conservé

bit rejeté

**5ème comparaison**

essai du bit 4

tension analogique associée

résultat comparaison

bit conservé

bit rejeté

**6ème comparaison**

essai du bit 3

tension analogique associée

résultat comparaison

bit conservé

bit rejeté

**7ème comparaison**

essai du bit 2

tension analogique associée

résultat comparaison

bit conservé

bit rejeté

**8ème comparaison**

essai du bit 1

tension analogique associée

résultat comparaison

bit conservé

bit rejeté

**Résultat des comparaisons successives:**

|                      |                      |                      |                      |                      |                      |                      |

|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| <input type="text"/> |

|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

**Vérification :**