## 1. Compteurs

### 11. Généralités

#### 111. Définition

Un compteur est un circuit logique séquentiel constitué d'un ensemble de  $n$  bascules interconnectées par des portes logiques. Il permet de dénombrer ou compter, suivant un système de numération binaire, le nombre d'impulsions appliquées à son entrée horloge : il reçoit les impulsions à compter et délivre en permanence en sa sortie une combinaison, des états logiques, image du nombre d'impulsions reçues.

#### 112. Classification des compteurs

En logique séquentielle, les compteurs peuvent être décrits en citant les caractéristiques suivantes :

**Sens de comptage** : Evolution de la valeur de sortie dans le temps.

➤ Comptage croissant ou ascendant  $\Rightarrow$  Compteurs.

➤ Comptage décroissant ou descendant  $\Rightarrow$  Décompteurs.

**Code de comptage** : Code dans lequel est exprimée la valeur de sortie.

Comptage en binaire naturel, en code Gray, en décimal, etc.

**Mode de comptage** : Type de basculement **asynchrone** ou **synchrone** du compteur.

Compteurs **asynchrones** ou compteurs **synchrone**s.

**Modulo de comptage** : Capacité du compteur exprimant le nombre d'états logiques différents que peut prendre la valeur de sortie sur l'ensemble du cycle de comptage.

Un compteur modulo  $M$  compte de 0 à  $(M-1)$  et comporte  $n$  bascules tel que :  $2^{n-1} < M \leq 2^n$ .

**Cycle de comptage** : précise si la valeur de sortie utilise ou non toutes les combinaisons possibles.

Comptage à cycle complet  $\Rightarrow M=2^n$  ou Comptage à cycle incomplet  $\Rightarrow M < 2^n$ .

## 12. Compteurs asynchrones

### 121. Définition

Un compteur asynchrone est constitué de  $n$  bascules JK fonctionnant en mode T (Toggle) :  $J=K=1$ . Ces bascules sont montées en cascade c'est-à-dire le signal d'horloge commande uniquement la première bascule tandis que pour chacune des autres bascules le signal d'horloge est fourni par la sortie de la bascule de rang immédiatement inférieur.

#### 122. Compteur asynchrone à cycle complet

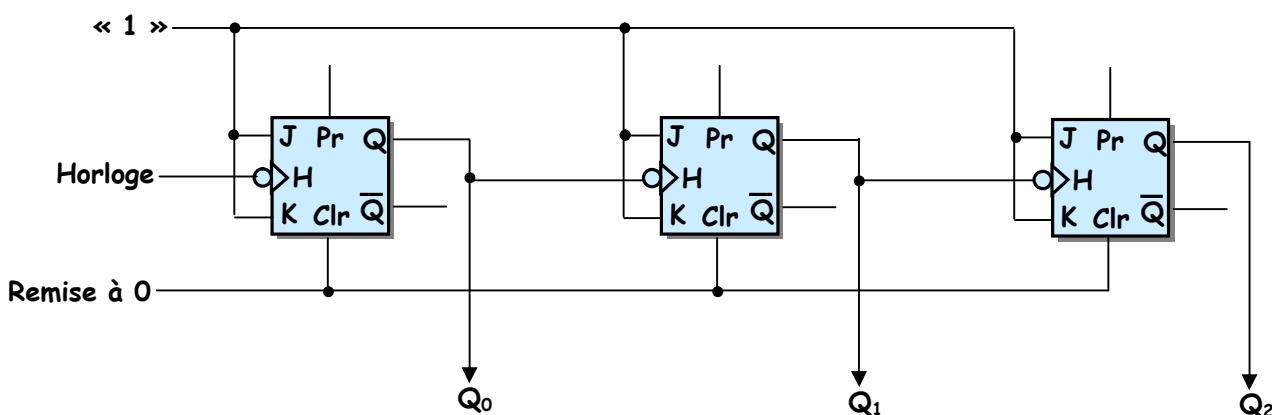

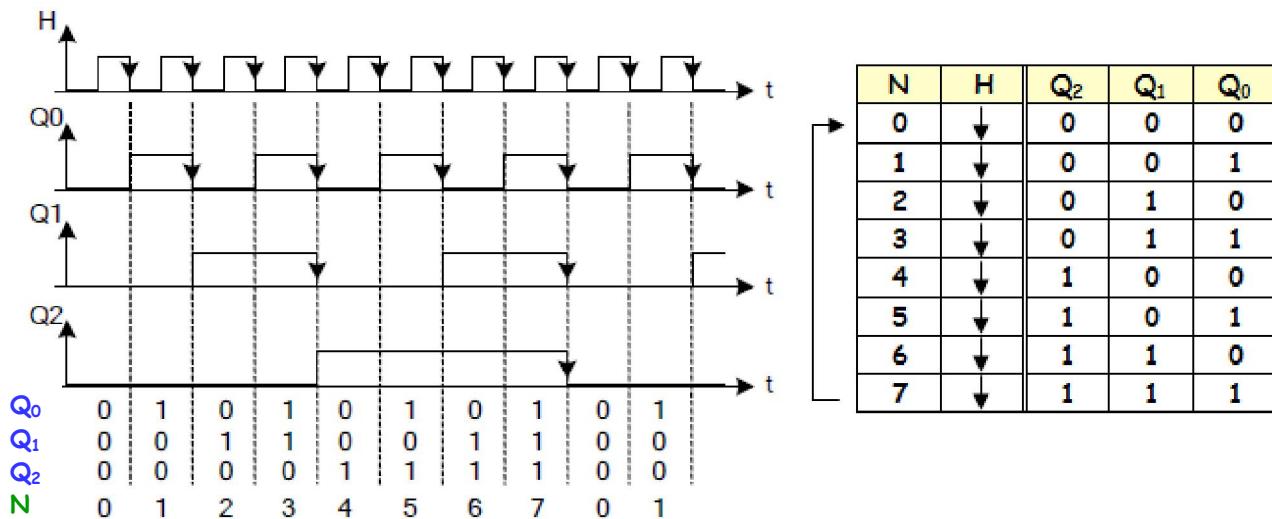

Pour bien comprendre le principe, réalisons un compteur **modulo 8** permettant de compter de 0 à 7.

Pour cela, on a besoin de 3 bascules JK montées de la manière suivante :

Les chronogrammes et la table de vérité d'un tel compteur sont donnés à la figure suivante :

### 123. Compteur asynchrone à cycle incomplet

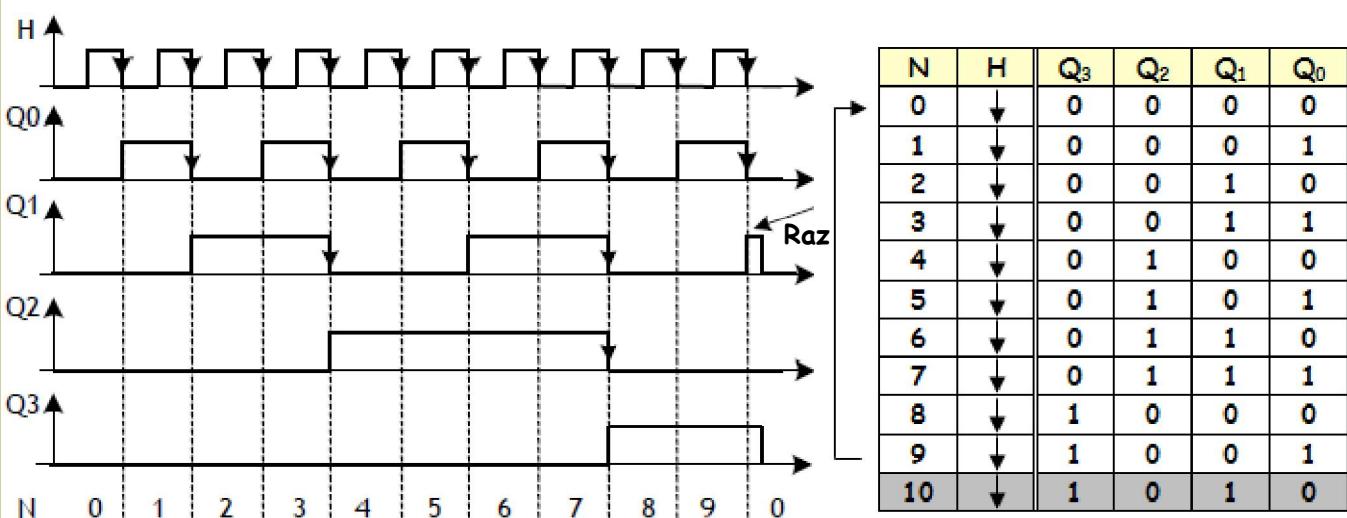

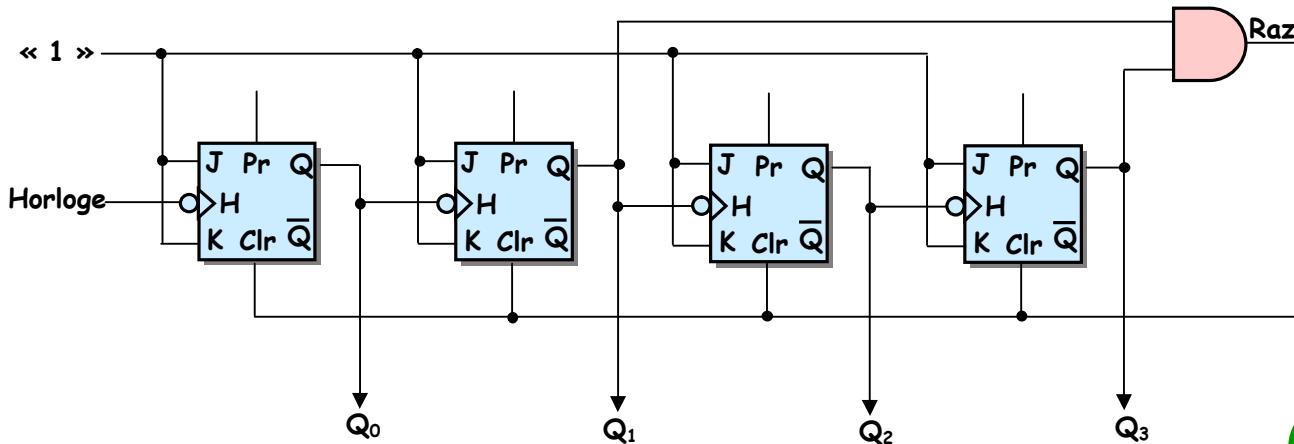

Soit à concevoir un compteur asynchrone **modulo 10** qui compte de 0 à 9.

Le nombre  $n$  des bascules nécessaires pour la réalisation du compteur est tel que :  $10 < 2^n$  soit  $n=4$ .

Avec 4 bascules, le modulo du compteur est 16 donc pour avoir un modulo 10 on procède à un **forçage à 0** du compteur à la combinaison  $N=10$  soit  $Q_3Q_2Q_1Q_0=1010$ .

Le forçage à 0 du compteur consiste à mettre à 0 toutes les sorties  $Q_i$  des 4 bascules.

On suppose que pour mettre  $Q_i$  à 0 on doit mettre l'entrée de forçage asynchrone  $Clr_i$  à 1.

Pour cela on cherche l'équation logique de l'entrée de commande, Remise à 0 **Raz**, en fonctions des  $Q_i$ .

| <b>Raz</b> | $Q_3$ | $Q_2$ | $Q_1$ | $Q_0$ |

|------------|-------|-------|-------|-------|

| $Q_3Q_2$   | 00    | 01    | 11    | 10    |

| 00         | 0     | 0     | 0     | 0     |

| 01         | 0     | 0     | 0     | 0     |

| 11         | X     | X     | X     | X     |

| 10         | 0     | 0     | X     | 1     |

Equation logique de l'entrée Raz

$Raz = Q_3Q_1$

Le câblage d'un tel compteur est donné par le schéma suivant :

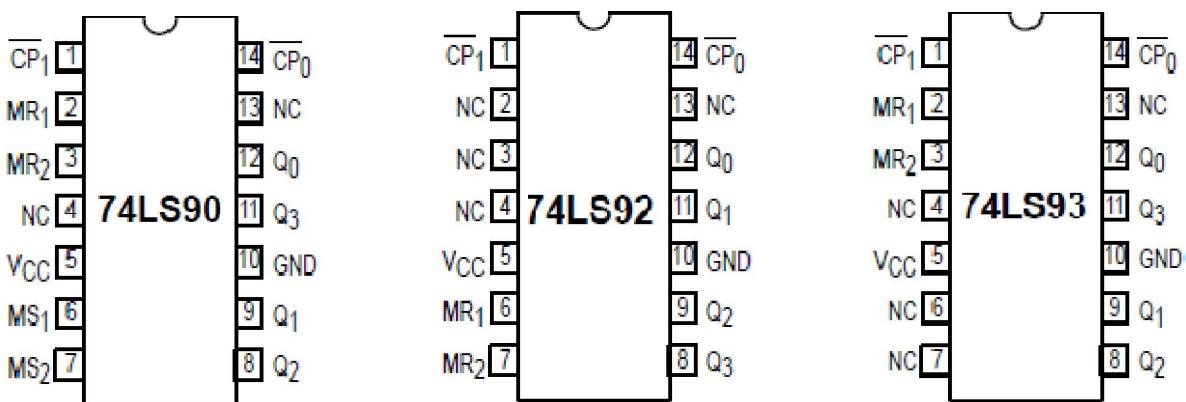

### 124. Compteurs asynchrones à circuits intégrés

Les compteurs 74LS90 (modulo 10), 74LS92 (modulo 12) et 74LS93 (modulo 16) sont des compteurs asynchrones composés de 4 bascules dont les connexions internes varient suivant le type du compteur.

**CP<sub>0</sub>** Clock (Active LOW going edge) Input to +2 Section

**CP<sub>1</sub>** Clock (Active LOW going edge) Input to +5 Section (LS90), +6 Section (LS92)

**CP<sub>1</sub>** Clock (Active LOW going edge) Input to +8 Section (LS93)

**MR<sub>1</sub>, MR<sub>2</sub>** Master Reset (Clear) Inputs

**MS<sub>1</sub>, MS<sub>2</sub>** Master Set (Preset-9, LS90) Inputs

**Q<sub>0</sub>** Output from +2 Section (Notes b & c)

**Q<sub>1</sub>, Q<sub>2</sub>, Q<sub>3</sub>** Outputs from +5 (LS90), +6 (LS92), +8 (LS93) Sections (Note b)

#### LS92 AND LS93 MODE SELECTION

| RESET INPUTS    |                 | OUTPUTS        |                |                |                |

|-----------------|-----------------|----------------|----------------|----------------|----------------|

| MR <sub>1</sub> | MR <sub>2</sub> | Q <sub>0</sub> | Q <sub>1</sub> | Q <sub>2</sub> | Q <sub>3</sub> |

| H               | H               | L              | L              | L              | L              |

| L               | H               | Count          |                |                |                |

| H               | L               | Count          |                |                |                |

| L               | L               | Count          |                |                |                |

Remarque :

La 1<sup>ère</sup> bascule, diviseur par 2, est séparée des 3 autres bascules qui sont interconnectées de telle sorte pour former un diviseur par 5 (74LS90), un diviseur par 6 (74LS92) et un diviseur par 8 (74LS93). Pour avoir un cycle de comptage modulo 10, 12 et 16 il faut relier le signal d'horloge externe à l'entrée **CP<sub>0</sub>** et la sortie **Q<sub>0</sub>** à l'entrée **CP<sub>1</sub>**.

| RESET/SET INPUTS |                 |                 |                 | OUTPUTS        |                |                |                |

|------------------|-----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|

| MR <sub>1</sub>  | MR <sub>2</sub> | MS <sub>1</sub> | MS <sub>2</sub> | Q <sub>0</sub> | Q <sub>1</sub> | Q <sub>2</sub> | Q <sub>3</sub> |

| H                | H               | L               | X               | L              | L              | L              | L              |

| H                | H               | X               | L               | L              | L              | L              | L              |

| X                | X               | H               | H               | H              | L              | L              | H              |

| L                | X               | L               | X               | Count          |                |                |                |

| X                | L               | X               | L               | Count          |                |                |                |

| L                | X               | X               | L               | Count          |                |                |                |

| X                | L               | L               | X               | Count          |                |                |                |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Don't Care

| LS90<br>BCD COUNT SEQUENCE |                |                |                |                |

|----------------------------|----------------|----------------|----------------|----------------|

| COUNT                      | OUTPUT         |                |                |                |

|                            | Q <sub>0</sub> | Q <sub>1</sub> | Q <sub>2</sub> | Q <sub>3</sub> |

| 0                          | L              | L              | L              | L              |

| 1                          | H              | L              | L              | L              |

| 2                          | L              | H              | L              | L              |

| 3                          | H              | H              | L              | L              |

| 4                          | L              | L              | H              | L              |

| 5                          | H              | L              | H              | L              |

| 6                          | L              | H              | H              | L              |

| 7                          | H              | H              | H              | L              |

| 0                          | L              | L              | L              | II             |

| 9                          | II             | L              | L              | II             |

NOTE: Output Q<sub>0</sub> is connected to Input CP<sub>1</sub> for BCD count.

| LS92<br>TRUTH TABLE |                |                |                |                |

|---------------------|----------------|----------------|----------------|----------------|

| COUNT               | OUTPUT         |                |                |                |

|                     | Q <sub>0</sub> | Q <sub>1</sub> | Q <sub>2</sub> | Q <sub>3</sub> |

| 0                   | L              | L              | L              | L              |

| 1                   | H              | L              | L              | L              |

| 2                   | L              | H              | L              | L              |

| 3                   | H              | H              | L              | L              |

| 4                   | L              | L              | H              | L              |

| 5                   | H              | L              | H              | L              |

| 6                   | L              | L              | L              | H              |

| 7                   | H              | L              | L              | H              |

| 0                   | L              | II             | L              | II             |

| 9                   | II             | II             | L              | II             |

| 10                  | L              | L              | II             | II             |

| 11                  | H              | L              | H              | H              |

NOTE: Output Q<sub>0</sub> is connected to Input CP<sub>1</sub>.

| LS93<br>TRUTH TABLE |                |                |                |                |

|---------------------|----------------|----------------|----------------|----------------|

| COUNT               | OUTPUT         |                |                |                |

|                     | Q <sub>0</sub> | Q <sub>1</sub> | Q <sub>2</sub> | Q <sub>3</sub> |

| 0                   | L              | L              | L              | L              |

| 1                   | H              | L              | L              | L              |

| 2                   | L              | H              | L              | L              |

| 3                   | H              | H              | L              | L              |

| 4                   | L              | L              | H              | L              |

| 5                   | H              | L              | H              | L              |

| 6                   | L              | L              | L              | H              |

| 7                   | H              | L              | L              | H              |

| 0                   | L              | II             | L              | II             |

| 9                   | II             | II             | L              | II             |

| 10                  | L              | L              | II             | II             |

| 11                  | H              | L              | H              | H              |

NOTE: Output Q<sub>0</sub> is connected to Input CP<sub>1</sub>.

## 125. Spécificités des compteurs asynchrones

L'avantage des compteurs asynchrones se constitue à la conception et à la réalisation simple et facile par répétition de modules diviseurs de fréquence par 2 : mise en cascade des bascules T.

Dans la structure asynchrone, les bascules commutent en cascade à partir d'un signal d'horloge affecté à la première bascule ce qui entraîne les inconvénients suivants :

- Un fonctionnement lent du compteur : pour  $n$  bascules en cascade, le temps de fonctionnement ou de propagation vaut  $n$  fois le temps de réponse (retard ou temps de propagation) d'une bascule.

- L'apparition des états de sortie erronés (**Glitches**) qui peuvent perturber le fonctionnement du système. Ces états transitoires parasites sont appelés des aléas du fonctionnement (nombres hors comptage). Par exemple, pour 3 bits, le passage de 011 à 100 est accompagné des états parasites 010 et 000. Le temps de réponse total lors de cette transition vaut 3 fois le temps de réponse d'une bascule.

## 13. Compteurs synchrones

### 131. Définition

Un compteur synchrone est constitué de  $n$  bascules qui reçoivent en parallèle le même signal d'horloge. L'entrée horloge est donc commune à toutes les bascules dont les sorties changent d'états simultanément.

### 132. Table d'excitation de la bascule JK

Elle permet de déterminer quelles valeurs il faut appliquer aux entrées synchrones J et K pour faire évoluer la sortie Q de la bascule d'un état vers un autre.

On note respectivement Q<sup>-</sup> et Q<sup>+</sup> les valeurs de Q avant et après l'impulsion d'horloge.

| Table de vérité |   |                |                |             |

|-----------------|---|----------------|----------------|-------------|

| J               | K | Q <sup>-</sup> | Q <sup>+</sup> | Commentaire |

| 0               | 0 | 0              | 0              | Mémoire     |

| 0               | 0 | 1              | 1              |             |

| 0               | 1 | 0              | 0              | Mise à 0    |

| 0               | 1 | 1              | 0              |             |

| 1               | 0 | 0              | 1              | Mise à 1    |

| 1               | 0 | 1              | 1              |             |

| 1               | 1 | 0              | 1              | Basculement |

| 1               | 1 | 1              | 0              |             |

| Table d'excitation |                |   |   |

|--------------------|----------------|---|---|

| Q <sup>-</sup>     | Q <sup>+</sup> | J | K |

| 0                  | 0              | 0 | X |

| 0                  | 1              | 1 | X |

| 1                  | 0              | X | 1 |

| 1                  | 1              | X | 0 |

X : Quelque soit l'état logique.

### 133. Compteur synchrone à cycle complet

Pour faire décrire au compteur une séquence déterminée il faut à chaque impulsion d'horloge définir les valeurs des entrées synchrones  $J$  et  $K$ . Pour cela on utilise la table de transition de la bascule  $JK$  ainsi que la table des états décrivant les différentes séquences du compteur.

La résolution du problème consiste donc à chercher les équations logiques des entrées  $J$  et  $K$  de chaque bascule à l'aide de la table des états recherchés et de la table d'excitation de la bascule  $JK$ .

Prenons l'exemple d'un compteur synchrone modulo 8.

| $J_0$ | $Q_1 Q_0$      | 00 | 01 | 11 | 10 |

|-------|----------------|----|----|----|----|

| 0     | Q <sub>2</sub> | 1  | X  | X  | 1  |

| 1     | Q <sub>2</sub> | 1  | X  | X  | 1  |

| $K_0$ | $Q_1 Q_0$      | 00 | 01 | 11 | 10 |

|-------|----------------|----|----|----|----|

| 0     | Q <sub>2</sub> | X  | 1  | 1  | X  |

| 1     | Q <sub>2</sub> | X  | 1  | 1  | X  |

| $J_1$ | $Q_1 Q_0$      | 00 | 01 | 11 | 10 |

|-------|----------------|----|----|----|----|

| 0     | Q <sub>2</sub> | 0  | 1  | X  | X  |

| 1     | Q <sub>2</sub> | 0  | 1  | X  | X  |

| $K_1$ | $Q_1 Q_0$      | 00 | 01 | 11 | 10 |

|-------|----------------|----|----|----|----|

| 0     | Q <sub>2</sub> | X  | X  | 1  | 0  |

| 1     | Q <sub>2</sub> | X  | X  | 1  | 0  |

| $J_2$ | $Q_1 Q_0$      | 00 | 01 | 11 | 10 |

|-------|----------------|----|----|----|----|

| 0     | Q <sub>2</sub> | 0  | 0  | 1  | 0  |

| 1     | Q <sub>2</sub> | X  | X  | X  | X  |

| $K_2$ | $Q_1 Q_0$      | 00 | 01 | 11 | 10 |

|-------|----------------|----|----|----|----|

| 0     | Q <sub>2</sub> | X  | X  | X  | X  |

| 1     | Q <sub>2</sub> | 0  | 0  | 1  | 0  |

Table des états du compteur

| $Q_1 Q_0$ | 00 | 01 | 11 | 10 |

|-----------|----|----|----|----|

| 0         | 0  | 1  | 3  | 2  |

| 1         | 4  | 5  | 7  | 6  |

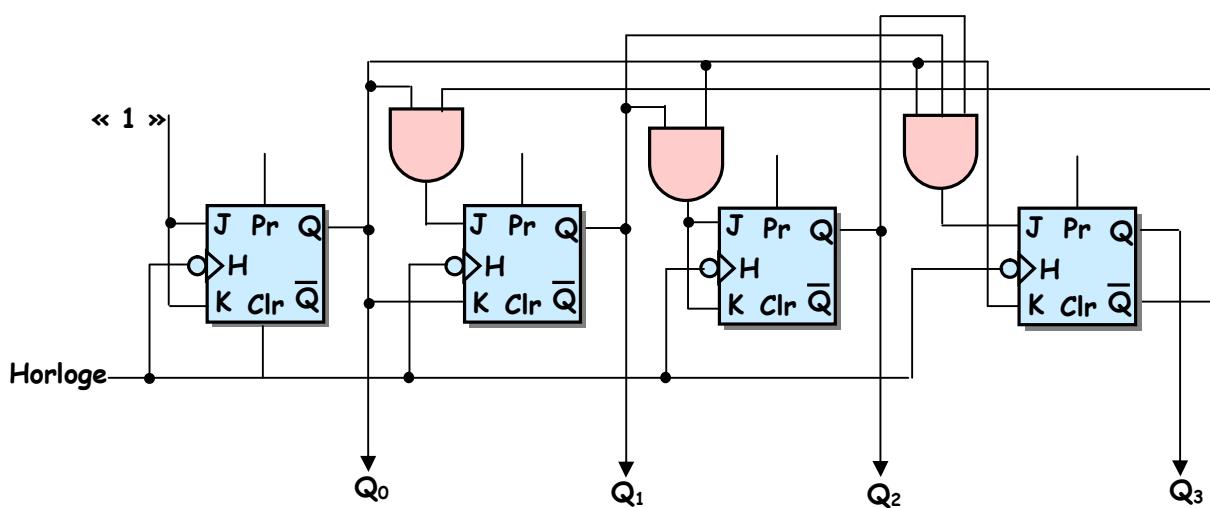

Equation logiques

$$J_0 = K_0 = 1$$

$$J_1 = K_1 = Q_0$$

$$J_2 = K_2 = Q_1 Q_0$$

Le câblage du compteur synchrone module 8 est donné par le schéma suivant :

### 134. Compteur synchrone à cycle incomplet

Soit à concevoir un compteur synchrone modulo 10.

Le nombre  $n$  des bascules nécessaires pour la réalisation du compteur est tel que :  $10 < 2^n$  soit  $n=4$ .

Table des états du compteur

| $Q_3 Q_2$ | 00 | 01 | 11 | 10 |

|-----------|----|----|----|----|

| 00        | 0  | 1  | 3  | 2  |

| 01        | 4  | 5  | 7  | 6  |

| 11        | X  | X  | X  | X  |

| 10        | 8  | 9  | X  | X  |

Les états à rejeter sont indiqués par des X

Equation logiques

$$J_0 = K_0 = 1$$

$$J_1 = \bar{Q}_3 Q_0$$

$$K_1 = Q_0$$

$$J_2 = K_2 = Q_1 Q_0$$

$$J_3 = Q_2 Q_1 Q_0$$

$$K_3 = Q_0$$

| $J_0$     | $Q_1 Q_0$ | 00 | 01 | 11 | 10 |

|-----------|-----------|----|----|----|----|

| $Q_3 Q_2$ | 00        | 1  | X  | X  | 1  |

| 01        | 1         | X  | X  | 1  |    |

| 11        | X         | X  | X  | X  |    |

| 10        | 1         | X  | X  | X  |    |

| $K_0$     | $Q_1 Q_0$ | 00 | 01 | 11 | 10 |

|-----------|-----------|----|----|----|----|

| $Q_3 Q_2$ | 00        | X  | 1  | 1  | X  |

| 01        | X         | 1  | 1  | X  |    |

| 11        | X         | X  | X  | X  |    |

| 10        | X         | 1  | X  | X  |    |

| $J_1$     | $Q_1 Q_0$ | 00 | 01 | 11 | 10 |

|-----------|-----------|----|----|----|----|

| $Q_3 Q_2$ | 00        | 0  | 1  | X  | X  |

| 01        | 0         | 1  | X  | X  |    |

| 11        | X         | X  | X  | X  |    |

| 10        | 0         | 0  | X  | X  |    |

| $K_1$     | $Q_1 Q_0$ | 00 | 01 | 11 | 10 |

|-----------|-----------|----|----|----|----|

| $Q_3 Q_2$ | 00        | X  | X  | 1  | 0  |

| 01        | X         | X  | 1  | 0  |    |

| 11        | X         | X  | X  | X  |    |

| 10        | X         | X  | X  | X  |    |

| $J_2$     | $Q_1 Q_0$ | 00 | 01 | 11 | 10 |

|-----------|-----------|----|----|----|----|

| $Q_3 Q_2$ | 00        | 0  | 0  | 1  | 0  |

| 01        | X         | X  | X  | X  |    |

| 11        | X         | X  | X  | X  |    |

| 10        | 0         | 0  | X  | X  |    |

| $K_2$     | $Q_1 Q_0$ | 00 | 01 | 11 | 10 |

|-----------|-----------|----|----|----|----|

| $Q_3 Q_2$ | 00        | X  | X  | X  | X  |

| 01        | 0         | 0  | 1  | 0  |    |

| 11        | X         | X  | X  | X  |    |

| 10        | X         | X  | X  | X  |    |

| $J_3$     | $Q_1 Q_0$ | 00 | 01 | 11 | 10 |

|-----------|-----------|----|----|----|----|

| $Q_3 Q_2$ | 00        | 0  | 0  | 0  | 0  |

| 01        | 0         | 0  | 1  | 0  |    |

| 11        | X         | X  | X  | X  |    |

| 10        | X         | X  | X  | X  |    |

| $K_3$     | $Q_1 Q_0$ | 00 | 01 | 11 | 10 |

|-----------|-----------|----|----|----|----|

| $Q_3 Q_2$ | 00        | X  | X  | X  | X  |

| 01        | X         | X  | X  | X  |    |

| 11        | X         | X  | X  | X  |    |

| 10        | 0         | 1  | X  | X  |    |

Le câblage du compteur synchrone module 10 est donné par le schéma suivant :

## 135. Spécificités des compteurs synchrones

### Avantages :

- Temps d'établissement constant (Une unité de propagation).

- Pas de valeurs parasites.

### Inconvénients :

- Utilisation des circuits logiques combinatoires en plus des bascules.

- Les modules sont donc différents.

## 136. Compteurs Spéciaux

### Compteurs réversibles

Ce sont des compteurs/décompteurs qui peuvent compter comme ils peuvent décompter. Le choix de la fonction comptage ou de la fonction décomptage s'effectue à l'aide d'une entrée de sélection.

### Compteurs programmables ou pré-positionnés (presettable)

Ce sont des compteurs possédant des entrées de pré-chargement qui contiennent la valeur de départ du comptage ou de décomptage. Le chargement du compteur se fait grâce à une entrée de commande.

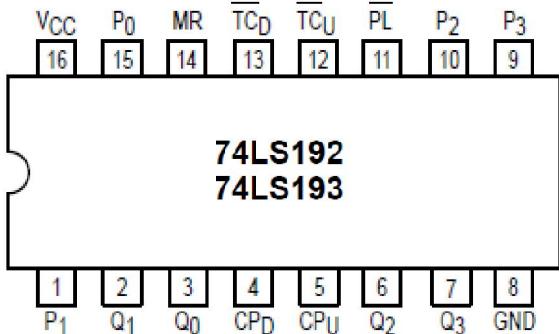

## 137. Compteurs synchrones à circuits intégrés

On cite à titre d'exemple :

- Les compteurs synchrones pré-positionnés modulo 10 : 74LS160 et 74LS162.

- Les compteurs synchrones pré-positionnés modulo 16 : 74LS161 et 74LS163.

- Les compteurs/décompteurs synchrones pré-positionnés modulo 10 : 74LS190 et 74LS192.

- Les compteurs/décompteurs synchrones pré-positionnés modulo 16 : 74LS191 et 74LS193.

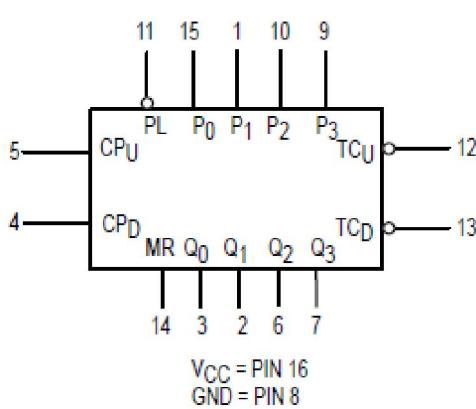

### CONNECTION DIAGRAM DIP

|                 |                                               |

|-----------------|-----------------------------------------------|

| CP <sub>U</sub> | Count Up Clock Pulse Input                    |

| CP <sub>D</sub> | Count Down Clock Pulse Input                  |

| MR              | Asynchronous Master Reset (Clear) Input       |

| PL              | Asynchronous Parallel Load (Active LOW) Input |

| P <sub>n</sub>  | Parallel Data Inputs                          |

| Q <sub>n</sub>  | Flip-Flop Outputs (Note b)                    |

| TCD             | Terminal Count Down (Borrow) Output (Note b)  |

| TCU             | Terminal Count Up (Carry) Output (Note b)     |

### LOGIC SYMBOL

### MODE SELECT TABLE

| MR | PL | CP <sub>U</sub> | CP <sub>D</sub> | MODE           |

|----|----|-----------------|-----------------|----------------|

| H  | X  | X               | X               | Reset (Asyn.)  |

| L  | L  | X               | X               | Preset (Asyn.) |

| L  | H  | H               | H               | No Change      |

| L  | H  | ⊓               | H               | Count Up       |

| L  | H  | H               | ⊓               | Count Down     |

L = LOW Voltage Level

H = HIGH Voltage Level

X = Don't Care

⊓ = LOW-to-HIGH Clock Transition

## 2. Registres à décalage

### 21. Définition

Un registre à décalage est une association en cascade de bascules D qui sont interconnectées de façon à ce que l'état logique de la bascule de rang  $i$  puisse être transmis à la bascule de rang  $i+1$  (décalage à droite) ou  $i-1$  (décalage à gauche) quand un signal d'horloge est appliqué à l'ensemble des bascules.

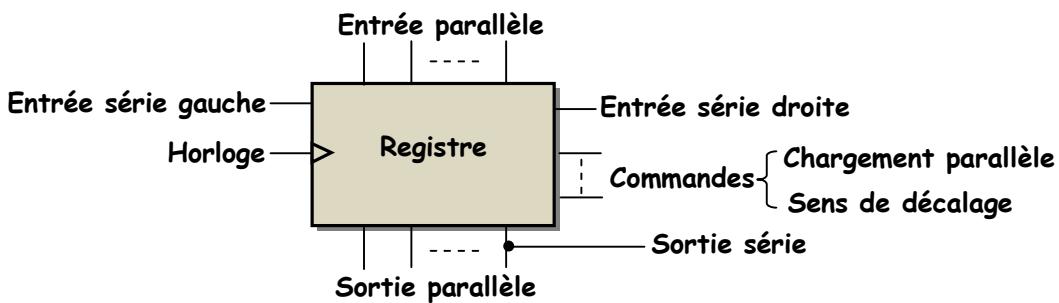

### 22. Classification des registres à décalage

En logique séquentielle, les registres à décalage se distinguent selon les caractéristiques suivantes :

#### 221. Type de décalage

L'information (une série de bits de donnée) peut être sérialisée suivant une direction de décalage à droite, à gauche ou dans ces deux directions (registre bidirectionnel).

#### 222. Type de chargement ou mode d'écriture

L'information peut être chargée selon un mode d'écriture série ou parallèle. En mode parallèle, la donnée est chargée dans les bascules d'un seul coup d'horloge (registre de mémorisation). En mode série, la donnée est présentée séquentiellement bit après bit à l'entrée de la première bascule, le décalage peut être alors vers la gauche ou la droite.

Pour le chargement série, ou aura un 1<sup>er</sup> chargement et une suite de décalages et chargements.

#### 223. Mode de lecture

De même, l'information peut être lue en série ou en parallèle.

#### 224. Nombre de bits

Le nombre de bits dans les registres est de **4, 5 ou 8**. Un registre composé de ces registres élémentaires peut contenir tout nombre de bits désiré.

## 23. Types des registres à décalage

- Registres à entrée parallèle et à sortie parallèle : Chargement parallèle ou mémorisation de la donnée.

- Registres à entrée parallèle et à sortie série : Chargement parallèle puis décalage de la donnée.

- Registres à entrée série et à sortie série : Chargement série puis décalage de la donnée.

- Registres à entrée série et à sortie parallèle : Chargement série puis décalage de la donnée.

- Les registres **universels** rassemblent les 4 modes de fonctionnement décrits ci-dessus.

Leur structure est donnée par le schéma synoptique suivant :

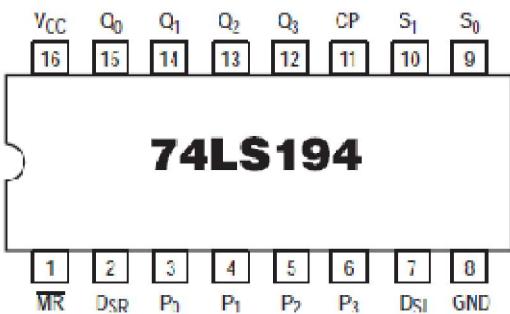

## 24. Registres à décalage à circuits intégrés

74LS194 est un registre à décalage universel de 4 bits.

Il est utilisé en modes série-série avec un décalage à gauche ou à droite, série-parallèle, parallèle-série et parallèle-parallèle.

|             |                                      |

|-------------|--------------------------------------|

| $S_0, S_1$  | Mode Control Inputs                  |

| $P_0 - P_3$ | Parallel Data Inputs                 |

| $D_{SR}$    | Serial (Shift Right) Data Input      |

| $D_{SL}$    | Serial (Shift Left) Data Input       |

| CP          | Clock (Active HIGH Going Edge) Input |

| MR          | Master Reset (Active LOW) Input      |

| $Q_0 - Q_3$ | Parallel Outputs                     |

MODE SELECT — TRUTH TABLE

| OPERATING MODE | INPUTS |       |       |          |          |       | OUTPUTS |       |       |       |

|----------------|--------|-------|-------|----------|----------|-------|---------|-------|-------|-------|

|                | MR     | $S_1$ | $S_0$ | $D_{SR}$ | $D_{SL}$ | $P_n$ | $Q_0$   | $Q_1$ | $Q_2$ | $Q_3$ |

| Reset          | L      | X     | X     | X        | X        | X     | L       | L     | L     | L     |

| Hold           | H      | I     | I     | X        | X        | X     | $q_0$   | $q_1$ | $q_2$ | $q_3$ |

| Shift Left     | H      | h     | I     | X        | I        | X     | $q_1$   | $q_2$ | $q_3$ | L     |

|                | H      | h     | I     | X        | h        | X     | $q_1$   | $q_2$ | $q_3$ | H     |

| Shift Right    | H      | I     | h     | I        | X        | X     | L       | $q_0$ | $q_1$ | $q_2$ |

|                | H      | I     | h     | h        | X        | X     | H       | $q_0$ | $q_1$ | $q_2$ |

| Parallel Load  | H      | h     | h     | X        | X        | $P_n$ | $P_0$   | $P_1$ | $P_2$ | $P_3$ |

L = LOW Voltage Level

H = HIGH Voltage Level

X = Don't Care

I = LOW voltage level one set-up time prior to the LOW to HIGH clock transition

h = HIGH voltage level one set-up time prior to the LOW to HIGH clock transition

$P_n$  ( $q_n$ ) = Lower case letters indicate the state of the referenced input (or output) one set-up time prior to the LOW to HIGH clock transition.

## 25. Applications des registres à décalage

Les registres à décalage ont de nombreuses applications. Parmi celles-ci, on trouve :

### 251. Conversion parallèle-série

La conversion de données parallèle-série est utilisée pour la transmission de données lors de l'émission.

On prend des données binaires (généralement un octet) en parallèle et on les convertit en un train binaire série (74LS165).

### 252. Conversion série-parallèle

La conversion de données série-parallèle est utilisée pour la transmission de données lors de la réception.

On prend des bits en série et on les convertit (généralement sur un octet) en parallèle (74LS164).

### 253. Opérations arithmétiques

Les opérations arithmétiques de la multiplication et de la division utilisent la technique ou le principe de décalage. On entre et on sort alors en parallèle.

### 254. Compteurs circulaires

Les compteurs circulaires sont des registres à décalage rebouclés (rétroaction) utilisés en mode série-série. Ils sont réalisés en connectant la sortie de la dernière bascule à l'entrée de la première bascule.

Pour cela, il faut effectuer un chargement initial du compteur-registre, puis à chaque coup d'horloge le contenu se décale en suivant une permutation circulaire.

On peut réaliser ainsi des compteurs en anneau, des compteurs Johnson, des chenillards (jeux de lumière), des générateurs d'horloges décalées, des générateurs de séquences pseudo-aléatoires, etc.

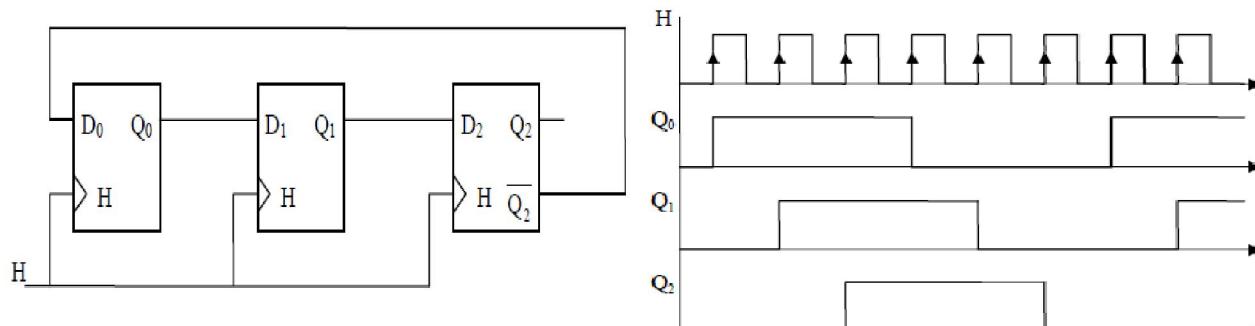

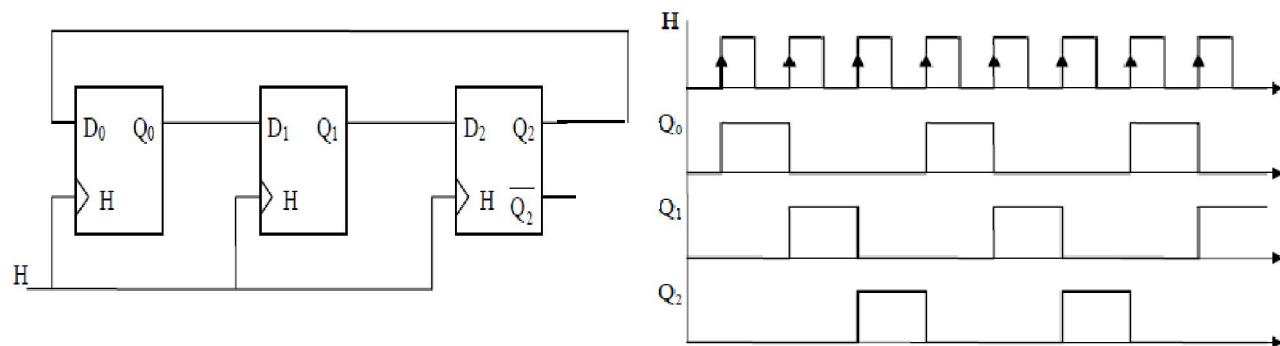

### Compteurs Johnson

Il est constitué de  $n$  bascules D en cascade en faisant un bouclage de la sortie complémentée de la dernière bascule avec l'entrée de la première bascule. Les bascules doivent être mises à 0 à la mise sous tension. On obtient des horloges de mêmes périodes, mais décalées en phase. Il s'agit d'un code jointif comme le code Gray car il n'y a qu'une sortie qui change à chaque coup d'horloge.

Pour comprendre le principe, considérons l'exemple suivant de 3 bascules D.

Fonction Traiter

### Compteurs en anneau

Il est constitué de  $n$  bascules D en cascade en faisant un bouclage de la sortie de la dernière bascule avec l'entrée de la première bascule. Il faut mettre à 1 une des bascules à la mise sous tension et les autres bascules sont mises à 0. On obtient ainsi des horloges décalées à temps jointifs.

Pour comprendre le principe, considérons l'exemple suivant de 3 bascules D. C'est un compteur 1 parmi 3. Le schéma est identique au précédent avec l'entrée D0 connectée à la sortie Q2.

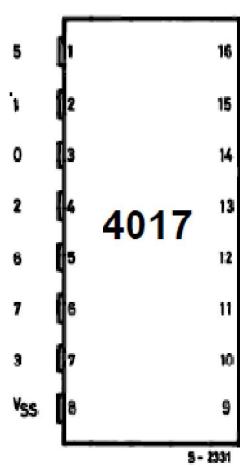

### Compteur Johnson à circuit intégré : 4017

| PIN No                         | SYMBOL          | NAME AND FUNCTION       |

|--------------------------------|-----------------|-------------------------|

| 3, 2, 4, 7, 10, 1, 5, 6, 9, 11 | 0 to 9          | Decoded Decimal Output  |

| 14                             | CLOCK           | Clock Input             |

| 13                             | CLOCK INHIBIT   | Clock Inhibit Input     |

| 15                             | RESET           | Reset Input             |

| 12                             | CARRY OUT       | Carry Output            |

| 8                              | V <sub>SS</sub> | Negative Supply Voltage |

| 16                             | V <sub>DD</sub> | Positive Supply Voltage |

| CLOCK | CLOCK INHIBIT | RESET | DECODED OUTPUT   |

|-------|---------------|-------|------------------|

| X     | X             | H     | Q <sub>0</sub>   |

| L     | X             | L     | Q <sub>0</sub>   |

| X     | H             | L     | Q <sub>1</sub>   |

| —     | L             | L     | Q <sub>n+1</sub> |

| —     | L             | L     | Q <sub>n</sub>   |

| H     | —             | I     | Q <sub>n</sub>   |

| H     | —             | L     | Q <sub>n+1</sub> |

X : Don't Care

Q<sub>n</sub> : No Change

### 3. Mémoires

#### 31. Définition

Une mémoire est un circuit à semi-conducteur permettant d'enregistrer, de conserver et de restituer des informations. Il y a **écriture** lorsqu'on enregistre des informations en mémoire et **lecture** lorsqu'on récupère des informations précédemment enregistrées.

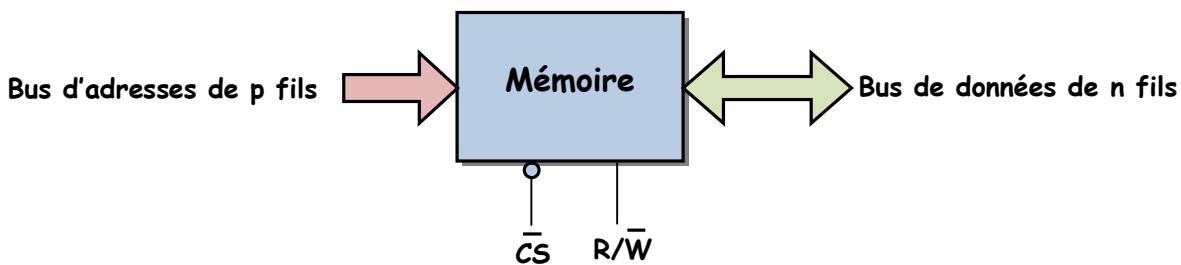

#### 32. Schéma fonctionnel d'une mémoire

Le schéma fonctionnel d'une mémoire est donné par le synoptique suivant :

**Notion de bus :** Un bus est un ensemble de fils.

Le bus d'adresses est un bus unidirectionnel et le bus de données est un bus bidirectionnel.

L'adresse fournie par le bus d'adresses est le mot binaire de **p** bits qui permet de localiser la donnée.

La donnée de **n** bits peut être écrite dans la mémoire ou lue de la mémoire à travers le bus de données.

Le choix entre le mode de lecture ou d'écriture se fait à l'aide de l'entrée **R/W** (Read/Write).

L'entrée de commande **CS** permet de sélectionner le circuit ou de le mettre en état de haute impédance.

La mémoire peut stocker  $2^p$  données de **n** bits.

#### 33. Cycle de lecture/écriture de la mémoire

Une mémoire peut être utilisée soit en lecture soit en écriture.

L'opération de **lecture** d'une mémoire suit le cycle suivant :

- Ecrire l'adresse de la donnée sur le bus d'adresses.

- Sélectionner le boîtier de la mémoire en appliquant un niveau logique **bas** sur l'entrée de commande **CS**.

- Choisir le mode de lecture en appliquant un niveau logique **haut** sur l'entrée de commande **R/W**.

- Lire la donnée sur le bus de données.

L'opération de **écriture** dans une mémoire suit le cycle suivant :

- Ecrire l'adresse de la donnée sur le bus d'adresses.

- Sélectionner le boîtier de la mémoire en appliquant un niveau logique **bas** sur l'entrée de commande **CS**.

- Choisir le mode d'écriture en appliquant un niveau logique **bas** sur l'entrée de commande **R/W**.

- Ecrire la donnée sur le bus de données.

#### 34. Caractéristiques d'une mémoire

##### 341. Capacité

C'est le nombre total de bits que contient la mémoire. Elle s'exprime aussi souvent en octets. Par exemple : 64b (b : bit), 4Kb, 8Ko (o : octet) avec :  $1 \text{ octet} = 8 \text{ bits}$ ,  $1K = 2^{10} = 1024$ ,  $1M = 2^{20} = 1024 \text{ K}$ ,  $1G = 2^{30} = 1024 \text{ M}$ .

##### 342. Format des données

C'est le nombre de bits que l'on peut mémoriser par case mémoire. On dit aussi que c'est la largeur du mot mémorisable.

### 343. Organisation

Elle définit le nombre de mots et la largeur de chaque mot. Par exemple :

- Une mémoire de 64Kx1 est constituée de 65536 mots de 1 bit. Sa capacité est donc de 64Kb (8Ko).

- Une mémoire de 8Kx8 contient 8192 mots de 8 bits. Sa capacité est donc de 64Kb (8Ko).

### 344. Temps d'accès

C'est le temps qui s'écoule entre l'instant où a été lancée une opération de lecture/écriture en mémoire et l'instant où l'information est effectivement disponible sur le bus de données.

### 345. Temps de cycle

Il représente l'intervalle minimum qui doit séparer deux demandes successives de lecture ou d'écriture.

### 346. Débit

C'est le nombre maximum d'informations lues ou écrites par seconde.

### 347. Volatilité

Elle caractérise la permanence des informations dans la mémoire. L'information stockée est volatile si elle risque d'être altérée par un défaut d'alimentation électrique et non volatile dans le cas contraire.

## 35. Différents types de mémoires

Les mémoires sont classées suivant deux familles :

- Mémoires mortes **ROM** (Read Only Memory) : mémoire à lecture seule.

- Mémoires vives **RAM** (Random Access Memory) : mémoire à lecture et écriture.

### 351. Mémoires vives

Une mémoire vive sert au stockage temporaire de données. Elle doit avoir un temps de cycle très court pour ne pas ralentir le microprocesseur. Les mémoires vives sont en général volatiles, elles perdent leurs informations en cas de coupure d'alimentation. Certaines d'entre elles, ayant une faible consommation, peuvent être rendues non volatiles par l'adjonction d'une batterie. Il existe deux grandes familles de mémoires **RAM** (mémoire à accès aléatoire) :

- Les **RAM statiques** : Le bit mémoire d'une RAM statique (**SRAM**) est composé d'une bascule. Chaque bascule contient entre 4 et 6 transistors.

- Les **RAM dynamiques** : Dans les RAM dynamiques (**DRAM**), l'information est mémorisée sous la forme d'une charge électrique stockée dans un condensateur (capacité grille substrat d'un transistor MOS).

### 352. Mémoires mortes

Pour certaines applications, il est nécessaire de pouvoir conserver des informations de façon permanente même lorsque l'alimentation électrique est interrompue. On utilise alors des mémoires mortes. Ces mémoires sont non volatiles. Contrairement aux RAM, ces mémoires ne peuvent être que lues. L'inscription des données en mémoire s'effectue par programmation. Suivant le type de la ROM, la méthode de la programmation changera. Il existe donc plusieurs types de ROM :

- **ROM** : Elle est programmée par le fabricant et son contenu ne peut plus être ni modifié, ni effacé par l'utilisateur.

- **PROM** : C'est une ROM qui peut être programmée une seule fois par l'utilisateur (**Programmable ROM**). La programmation est réalisée à partir d'un programmeur spécifique.

- **EPROM ou UV-EPROM** : Pour faciliter la mise au point d'un programme ou tout simplement permettre une erreur de programmation, il est intéressant de pouvoir reprogrammer une PROM. L'EPROM (Erasable Programmable ROM) est une PROM qui peut être effacée par des rayons ultra violets.

- **EEPROM** : Electrically EPROM est une mémoire programmable et effaçable électriquement et peut être programmée in situ.

- **FLASH EPROM** : La mémoire Flash s'apparente à la technologie de l'EEPROM. Elle est programmable et effaçable électriquement comme les EEPROM.

### 36. Extension de la capacité d'une mémoire

Il est courant dans un système microinformatique de grouper plusieurs circuits pour augmenter la capacité (nombre des mots et/ou longueur des mots). Par exemple, à l'aide de **4 boîtiers** mémoires de **1Kx4bits**, on peut réaliser les mémoires suivantes : **1Kx16bits**, **4Kx4bits**, **2Kx8bits**.

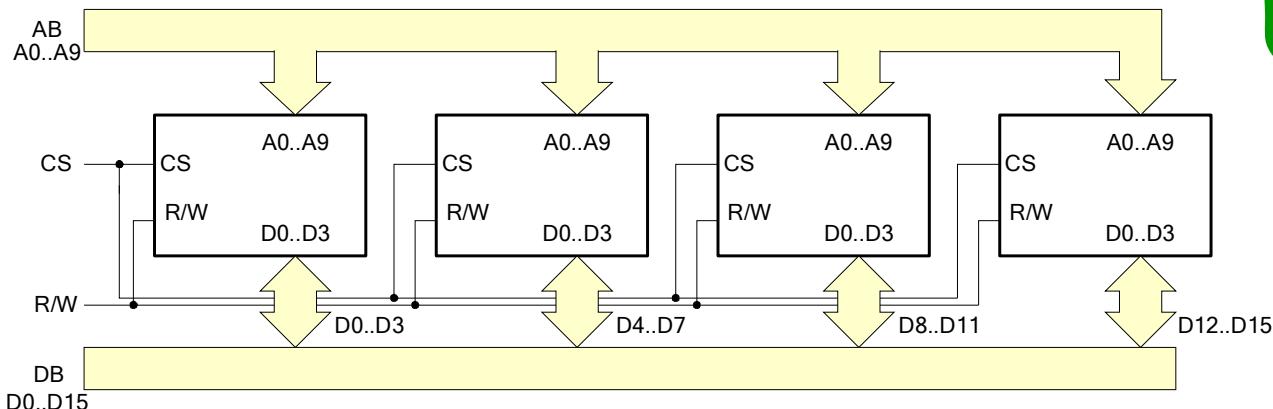

Le schéma ci-dessous réalise une mémoire de **1Kx16bits** (extension de format de la mémoire) à partir d'une mémoire élémentaire de **1Kx4bits** :

- Nécessité de **4 boîtiers**.

- Nécessité de **10 bits** d'adresses **A<sub>0</sub>** à **A<sub>9</sub>**.

- Nécessité de **16 bits** de données **D<sub>0</sub>** à **D<sub>15</sub>**.