## 1. Présentation d'un PLD

Les circuits logiques programmables(Programmable Logic Device ou en abrégé PLD) sont des circuits vierges disposant des entrées et des sorties dont l'utilisateur peut programmer le schéma logique d'après les besoins liés à la fonction logique souhaitée(cahier des charges) : Logique combinatoire et/ou séquentielle.

## 2. Structure de base d'un PLD

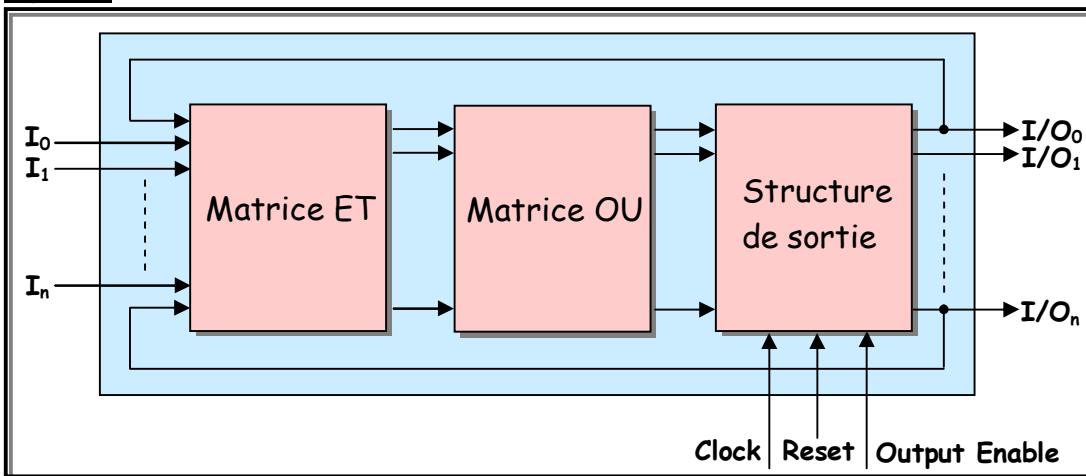

La plupart des PLDs suivent la structure de base de la figure 1 :

- Un ensemble d'opérateurs **ET** sur lesquels viennent se connecter les variables d'entrée et leurs compléments.

- Un ensemble d'opérateurs **OU** sur lesquels les sorties des opérateurs **ET** sont connectées.

- Une éventuelle structure de sortie : Portes inverseuses, Portes 3 états, Multiplieurs, Portes XOR, Bascules, ...etc.

Figure 1

L'ensemble des opérateurs forment des matrices(matrice **OU** et matrice **ET**). Ces deux matrices forment une structure appelée PLA(Programmable Logic Array) ou un réseau logique programmable.

Les interconnexions de ces matrices sont assurées par des fusibles qui sont « grillés » lors de la programmation. Lorsqu'un PLD est vierge toutes les connexions sont assurées(fusibles intacts).

La figure 2a illustre la structure interne d'un PLA à 2 variables d'entrée et 2 variables de sortie. La figure 2b donne la représentation simplifiée et conventionnelle d'une telle structure ayant ses fusibles intacts.

Les équations logiques de  $Q_0$  et  $Q_1$  sont  $Q_0=Q_1=0$ . Si on veut obtenir les fonctions logiques  $Q_0=a./b+/b.a$  et  $Q_1=a.b+/b./a$ , on « grillera » les fusibles de façon à obtenir le schéma de la figure 2c.

### Remarques :

- /x signifie x barre.

- La technique des fusibles est en voie de disparition : le PLD est programmé une seule fois.

- Actuellement la technique la plus répandue utilise le transistor **MOSFET** à la place du fusible. Cette technique permet de programmer et reprogrammer le PLD grâce à un effacement électrique.

Figure 2

Fonction Traiter

### 3. Classification des PLDs

Il existe plusieurs familles de PLD qui sont différenciées par leurs structures internes, la possibilité et la procédure d'effacement. Le tableau de la figure 3 représente deux classes de base de ces familles.

Figure 3

| Type | Densité         | Matrice ET   | Matrice OU | Effaçable      |

|------|-----------------|--------------|------------|----------------|

| PAL  | 10 à 100 portes | Programmable | Fixe       | Non            |

| GAL  | 10 à 100 portes | Programmable | Fixe       | Electriquement |

## 4. Les PALs(Programmable Array Logic)

### 41. Présentation

Les PALs sont les premiers circuits programmables à être utilisés et ont été développés par la société AMD il y a une vingtaine d'années. Ils possèdent une matrice ET programmable et une matrice OU fixe.

Les PALs sont programmés par destruction de fusibles et ne sont donc programmables qu'une seule fois. La fusion des fusibles est obtenue en appliquant à leurs bornes, à l'aide d'un programmeur adapté, une tension de 12 à 15 V pendant 10 à 50 µS.

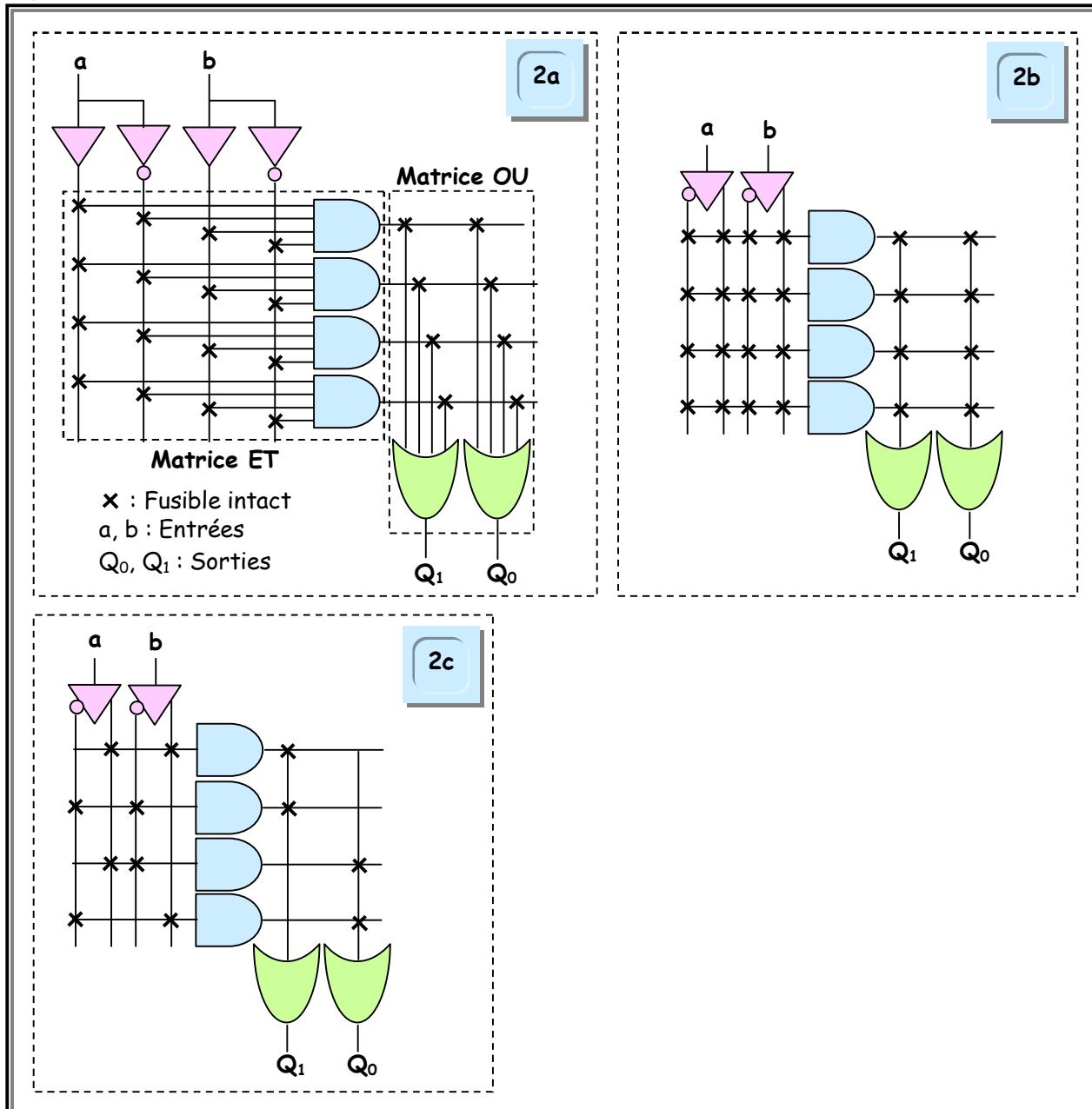

La figure 4a illustre la structure interne de base d'un PAL à 4 variables d'entrée et 2 variables de sortie.

Soit à programmer les fonctions logiques  $Q_0 = ab + bc + cd + da$  et  $Q_1 = abc + bcd + cda + dab$ .

On « grillera » les fusibles de façon à obtenir le schéma de la figure 4b.

Figure 4

Fonction Traiter

### 42. Les différents types de sortie d'un PAL

#### 421. Structure de sortie combinatoire

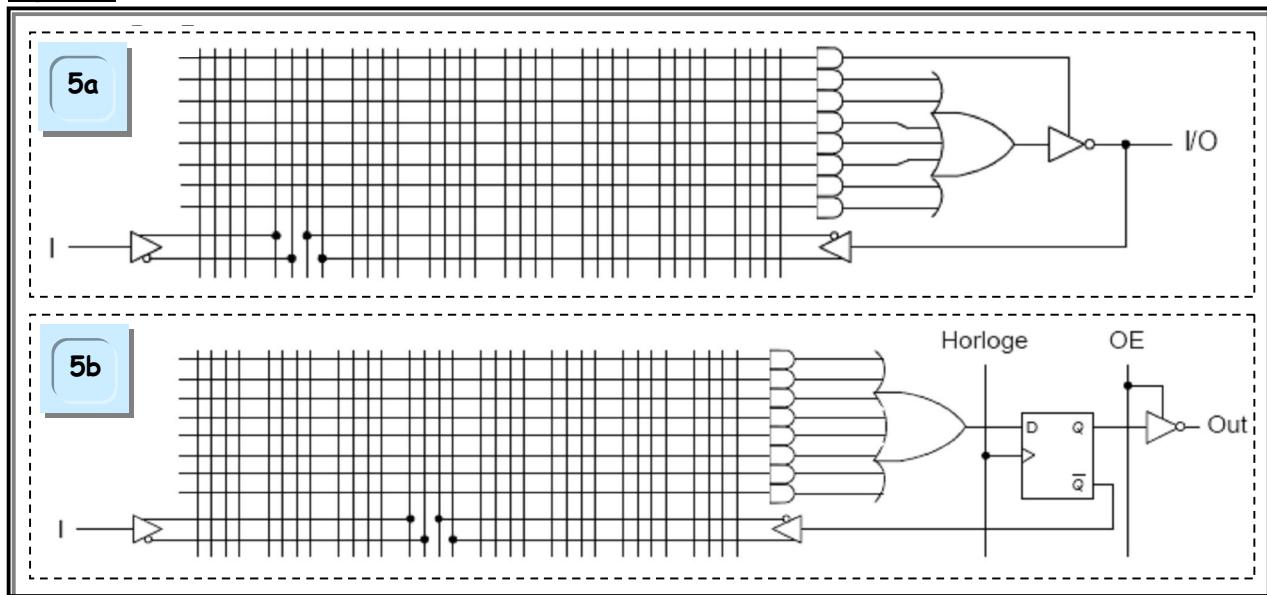

Certaines broches de sortie peuvent être configurées aussi bien en entrée qu'en sortie grâce à un système de logique 3 états. Ainsi, une broche de sortie peut être réinjectée en entrée.

La sortie peut être active à l'état bas comme le cas de la figure 5a(PAL de type L) ou à l'état haut(PAL de type H).

#### 422. Structure de sortie séquentielle

Ces sorties utilisent des bascules D dont les sorties sont de type trois états. Elles sont contrôlées par un signal de validation OE(Output Enable) et une horloge commune à toutes les bascules(PAL de type R).

La sortie peut être inversée comme le cas de la figure 5b ou non inversée.

Figure 5

### 423. Référence des PALs(D'après AMD)

Les constructeurs ont défini une nomenclature permettant de décoder facilement la référence des PALs.

Figure 6

| PAL (OE) XX AB YY C ZZ DEF |                            | Structure des sorties |                                 |

|----------------------------|----------------------------|-----------------------|---------------------------------|

| Code                       | Structure de sortie        | Code                  | Structure de sortie             |

| OE                         | Pour la version CMOS       | L                     | Combinatoire active bas         |

| XX                         | Nombre d'entrées (10 à 22) | H                     | Combinatoire active haut        |

| AB                         | Structure des sorties      | C                     | Combinatoire active bas ou haut |

| YY                         | Nombre de sorties (1 à 10) | R                     | Registre synchrone              |

| C                          | Consommation               | RA                    | Registre asynchrone             |

| ZZ                         | Vitesse en ns              | X                     | Registre et Ou exclusif         |

| DEF                        | Type de boîtier            | V                     | Versatile (programmable)        |

**Exemple d'un PAL 16 L 8 H 15 PC**

|    |                         |

|----|-------------------------|

| 16 | 16 entrées              |

| L  | Combinatoire active bas |

| 8  | 8 sorties               |

| H  | $\frac{1}{2}$ puissance |

| 15 | 15 ns                   |

| PC | DIL plastique civile    |

**PAL 16L8 :**

- 10 broches configurables uniquement en entrée.

- 2 broches configurables uniquement en sortie.

- 6 broches configurables en entrée ou en sortie.

- 2 broches d'alimentation.

**PAL 16R8 :**

- 8 broches configurables uniquement en entrée.

- 1 broche d'entrée horloge de l'ensemble des 8 bascules D.

- 1 broche de validation des 8 sorties(Output Enable).

- 8 broches configurables en sortie ou en entrée.

- 2 broches d'alimentation.

The pinouts show the following connections for each chip:

- PAL 16L8:** Pin 1: GND, Pin 2: I/O, Pin 3: I/O, Pin 4: I/O, Pin 5: I/O, Pin 6: I/O, Pin 7: I/O, Pin 8: I/O, Pin 9: I/O, Pin 10: OE, Pin 11: GND, Pin 12: O, Pin 13: I/O, Pin 14: I/O, Pin 15: I/O, Pin 16: I/O, Pin 17: I/O, Pin 18: I/O, Pin 19: O, Pin 20: V<sub>CC</sub>.

- PAL 16R8:** Pin 1: CLK, Pin 2: I/O, Pin 3: I/O, Pin 4: I/O, Pin 5: I/O, Pin 6: I/O, Pin 7: I/O, Pin 8: I/O, Pin 9: I/O, Pin 10: GND, Pin 11: OE, Pin 12: Q, Pin 13: Q, Pin 14: Q, Pin 15: Q, Pin 16: Q, Pin 17: Q, Pin 18: Q, Pin 19: Q, Pin 20: V<sub>CC</sub>.

## 5. Les GALs(Generic Array Logic)

L'inconvénient majeur d'un PAL est qu'il ne peut être programmé qu'une seule fois, ce qui impose un "gaspillage" lors du développement. La société **LATTICE** a remplacé les fusibles par les transistors **MOSFET** et a donné naissance aux **GALs**(Réseau logique générique).

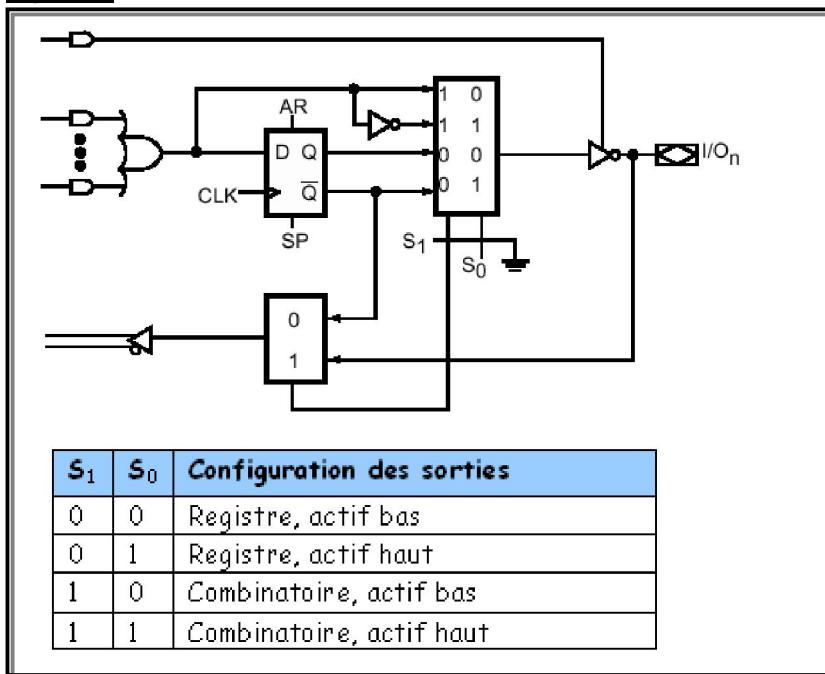

Les **GALs** sont donc des **PALs** effaçables, avec en plus des macro-cellules de sortie programmables, ce qui les rend **versatiles**. La partie nommée **OLMC**(OUTPUT LOGIC MACROCELL) est **versatile**, ce qui veut dire qu'il est possible par programmation de choisir entre une configuration de sortie combinatoire ou séquentielle.

La figure 7 montre la structure et la table de fonctionnement d'une OLMC :

- Le multiplexeur 4 vers 1 permet de mettre en circuit ou non la bascule D, en inversant ou non les signaux.

- Le multiplexeur 2 vers 1 permet de réinjecter soit la sortie, soit l'entrée du buffer de sortie vers la matrice.

Figure 7

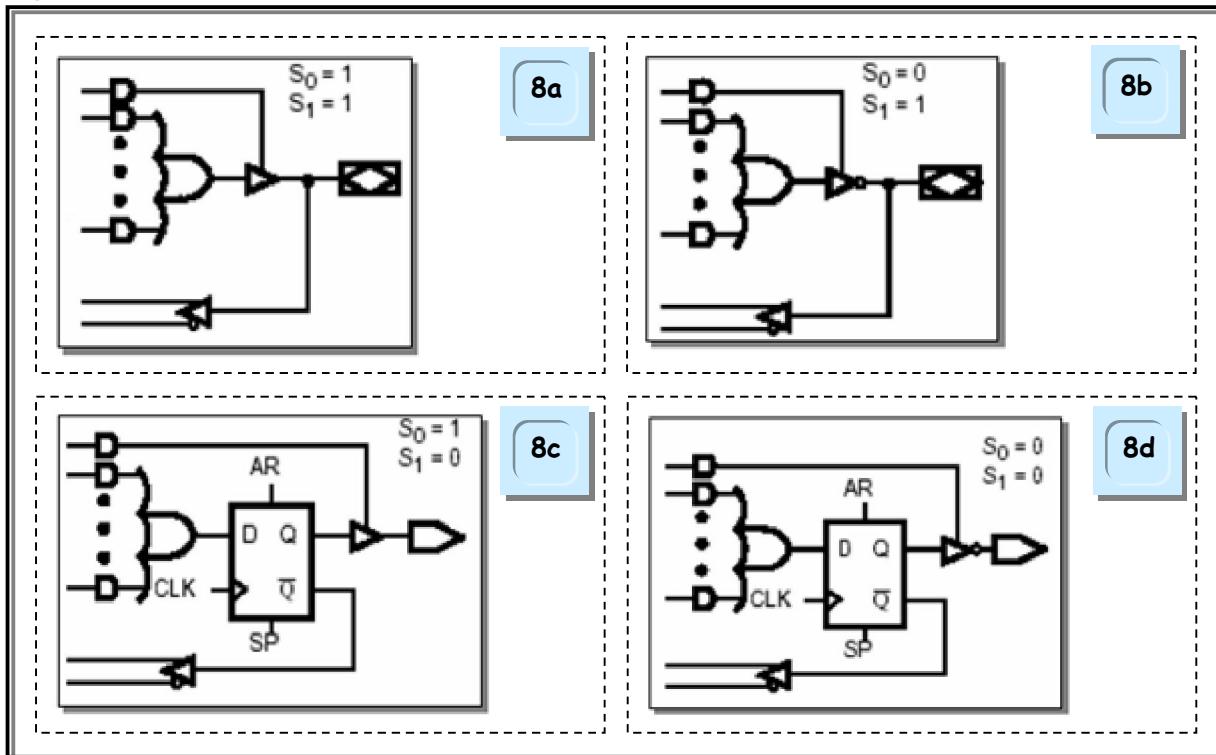

Ainsi on pourra avoir suivant chaque combinaison de  $S_0$  et  $S_1$  :

- La sortie est celle de l'opérateur OU : sortie combinatoire de type H(voir figure 8a).

- La sortie est complémentaire de l'opérateur OU : sortie combinatoire de type L(voir figure 8b).

- La sortie est celle de l'opérateur OU mémorisée par une bascule D sur les fronts montants de l'horloge CLK : sortie séquentielle de type R, active haut(voir figure 8c).

- La sortie est complémentaire de l'opérateur OU, mémorisée par une bascule D sur les fronts montants de l'horloge CLK : sortie séquentielle de type R, active bas(voir figure 8d).

Le schéma équivalent correspondant à chaque combinaison est représenté à la figure 8.

**Figure 8**

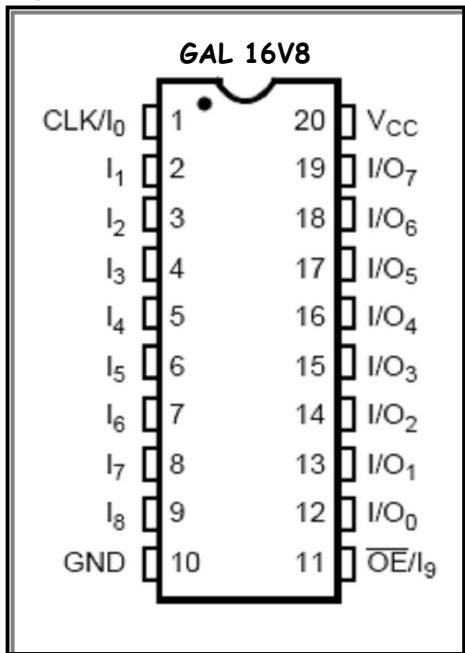

La figure 9 donne le brochage du **GAL 16V8** de la société LATTICE.

**Figure 9**